- 您现在的位置:买卖IC网 > PDF目录370013 > PowerNP NPe405H (IBM Microeletronics) 32-Bit Embedded Processor(32位嵌入式处理器) PDF资料下载

参数资料

| 型号: | PowerNP NPe405H |

| 厂商: | IBM Microeletronics |

| 英文描述: | 32-Bit Embedded Processor(32位嵌入式处理器) |

| 中文描述: | 32位嵌入式处理器(32位嵌入式处理器) |

| 文件页数: | 37/64页 |

| 文件大小: | 1050K |

| 代理商: | POWERNP NPE405H |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

Advance Information

PowerNP

TM

NPe405H Embedded Processor Data Sheet

37

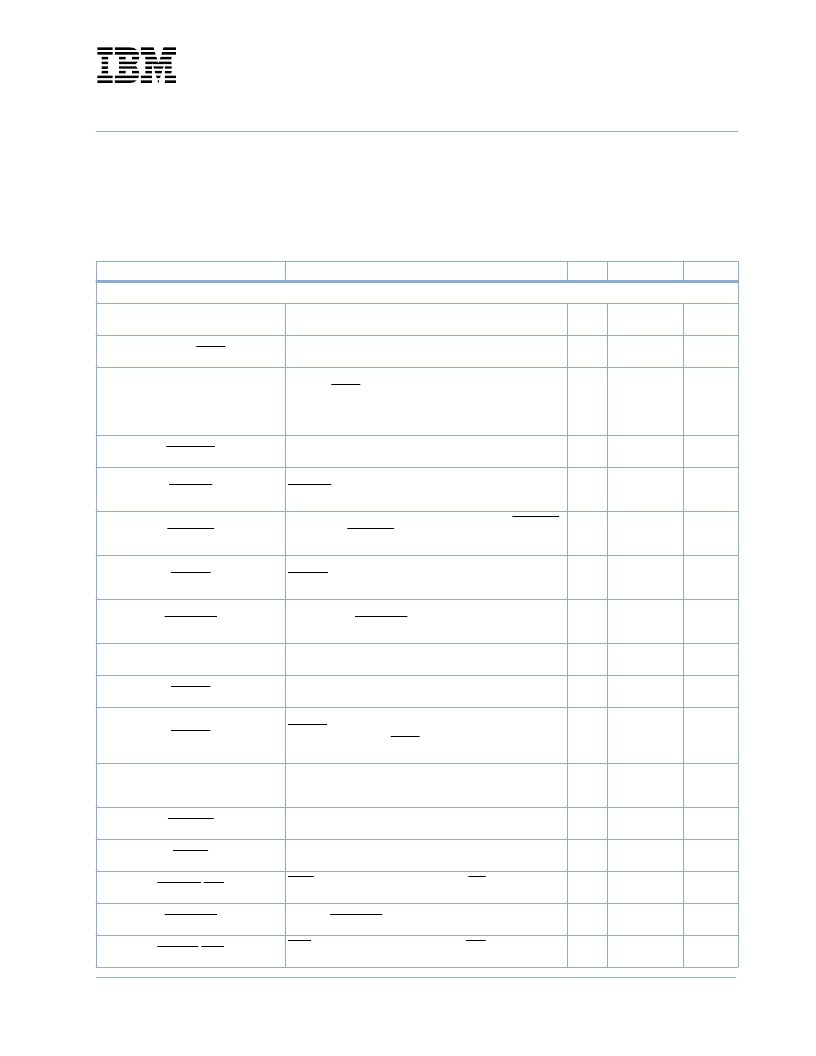

Signal Functional Description

(Part 1 of 9)

Notes:

1. Receiver input has hysteresis

2. Must pull up (recommended value is 3k

to 3.3V, 10k

to 5V

)

3. Must pull down (recommended value is 1k

)

4. If not used, must pull up (recommended value is 3k

to 3.3V)

5. If not used, must pull down (recommended value is 1k

)

Signal Name

Description

I/O

Type

Notes

PCI Interface

PCIAD0:31

PCI Address/Data bus. Multiplexed address and data bus

I/O

5V tolerant

3.3V PCI

4

PCIC0:3[BE0:3]

PCI bus command or Byte Enable

I/O

5V tolerant

3.3V PCI

4

PCIParity

PCI Parity. Parity is even across PCIAD0:31 and

PCIC0:3[BE0:3]. PCIParity is valid one cycle after either an

address or data phase. The PCI device that drove

PCIAD0:31 is responsible for driving PCIParity on the next

PCI bus clock.

I/O

5V tolerant

3.3V PCI

4

PCIFrame

Driven by the current PCI bus master to indicate beginning

and duration of a PCI access.

I/O

5V tolerant

3.3V PCI

4

PCIIRDY

Driven by the current PCI bus master. Assertion of

PCIIRDY indicates that the PCI initiator is ready to transfer

data.

I/O

5V tolerant

3.3V PCI

4

PCITRDY

The target of the current PCI transaction drives PCITRDY.

Assertion of PCITRDY indicates that the PCI target is

ready to transfer data.

I/O

5V tolerant

3.3V PCI

4

PCIStop

The target of the current PCI transaction can assert

PCIStop to indicate to the requesting PCI master that it

wants to end the current transaction.

I/O

5V tolerant

3.3V PCI

4

PCIDevSel

Driven by the target of the current PCI transaction. A PCI

target asserts PCIDevSel when it has decoded an address

and command encoding and claims the transaction.

I/O

5V tolerant

3.3V PCI

4

PCIIDSel

Used during configuration cycles to select the PCI slave

interface for configuration

I

5V tolerant

3.3V PCI

5

PCISErr

Used for reporting address parity errors or catastrophic

failures detected by a PCI target.

I/O

5V tolerant

3.3V PCI

4

PCIPErr

Used for reporting data parity errors on PCI transactions.

PCIPErr is driven active by the device receiving

PCIAD0:31, PCIC0:3[BE0:3], and PCIParity, two PCI

clocks following the data in which bad parity is detected.

I/O

5V tolerant

3.3V PCI

4

PCIClk

Used as the asynchronous PCI clock when in asynch

mode. It is unused when the PCI interface is operated

synchronously with the PLB bus.

I

5V tolerant

3.3V PCI

5

PCIReset

PCI specific reset

O

5V tolerant

3.3V PCI

PCIINT

PCI Interrupt. Open-drain output (two states; 0 or open

circuit).

O

5V tolerant

3.3V PCI

PCIReq0[Gnt]

Req0 when internal arbiter is used, or Gnt when external

arbiter is used.

I

5V tolerant

3.3V PCI

4

PCIReq1:5

Used as PCIReq1:5 input when internal arbiter is used

I

5V tolerant

3.3V PCI

4

PCIGnt0[Req]

Gnt0 when internal arbiter is used, or Req when external

arbiter is used

O

5V tolerant

3.3V PCI

相关PDF资料 |

PDF描述 |

|---|---|

| PowerNP NPe405L | 32-Bit Embedded Processor(32位嵌入式处理器) |

| PowerNP NPe405 | 32-Bit Embedded Processor(32位嵌入式处理器(应用于网络方面,提供高性价比)) |

| PowerPC 401GF | 32-bit RISC Embedded Controllers(32位RISC结构嵌入式控制器) |

| PowerPC 403GA | 32-bit RISC Embedded Controllers(32位RISC结构嵌入式控制器) |

| PowerPC 403GB | 32-bit RISC Embedded Controllers(32位RISC结构嵌入式控制器) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| POWERPAC-B | 制造商:IAR Systems 功能描述:PowerPac |

| POWERPAC-S | 制造商:IAR Systems 功能描述:PowerPac |

| POWERPAT PLUS | 制造商:Fluke Electronics 功能描述:SOFTWARE PAT |

| POWERPATPLUS | 制造商:Fluke Electronics 功能描述:Fluke Powerpat Plus |

| POWERPLUG15W | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:AC/DC POWER SUPPLY |

发布紧急采购,3分钟左右您将得到回复。