- 您现在的位置:买卖IC网 > PDF目录370013 > PowerNP NPe405H (IBM Microeletronics) 32-Bit Embedded Processor(32位嵌入式处理器) PDF资料下载

参数资料

| 型号: | PowerNP NPe405H |

| 厂商: | IBM Microeletronics |

| 英文描述: | 32-Bit Embedded Processor(32位嵌入式处理器) |

| 中文描述: | 32位嵌入式处理器(32位嵌入式处理器) |

| 文件页数: | 43/64页 |

| 文件大小: | 1050K |

| 代理商: | POWERNP NPE405H |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页当前第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

Advance Information

PowerNP

TM

NPe405H Embedded Processor Data Sheet

43

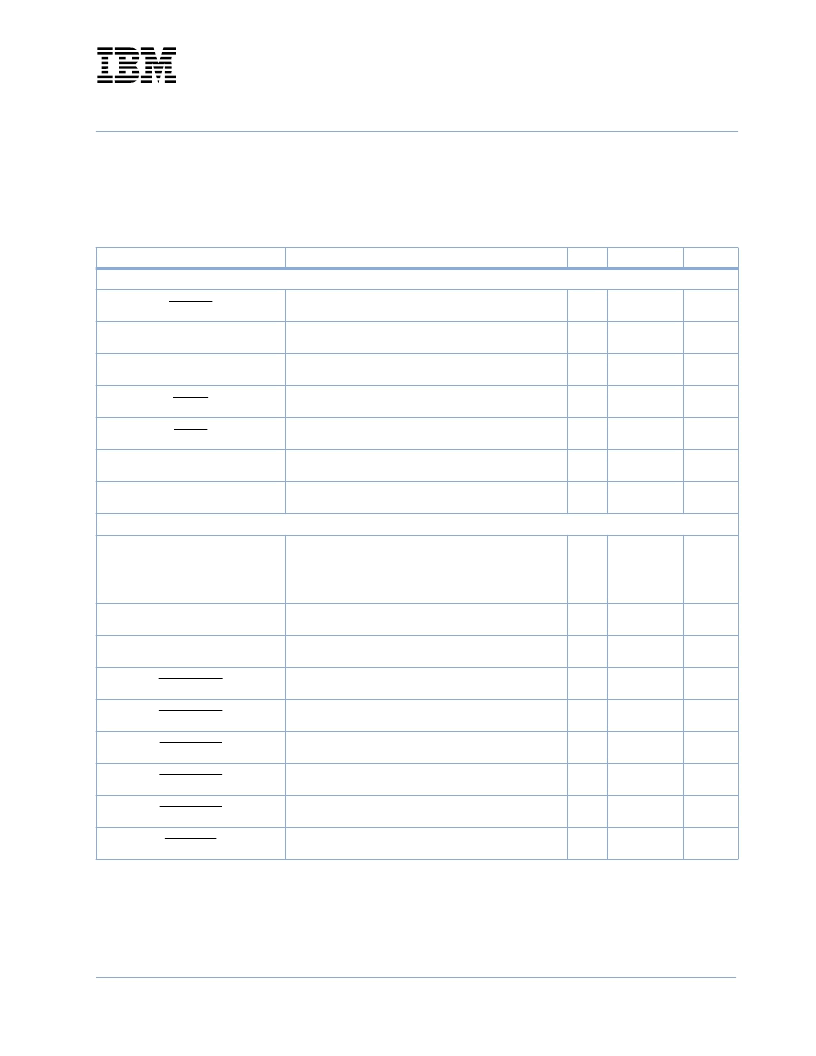

External Master Peripheral Interface

ExtReset

Peripheral Reset. Used by an external master and

synchronous peripheral slaves.

O

5V tolerant

3.3V LVTTL

HoldReq

Hold Request. Used by an external master to request

ownership of the peripheral bus.

I

5V tolerant

3.3V LVTTL

1, 5

HoldAck

Hold Acknowledge. Used by the NPe405H to transfer

ownership of peripheral bus to an external master.

O

5V tolerant

3.3V LVTTL

ExtReq

External Request. Used by an external master to indicate it

is prepared to transfer data.

I

5V tolerant

3.3V LVTTL

1, 4

ExtAck

Exteranl Acknowledgement. Used by the NPe405H to

indicate that a data transfer occurred.

O

5V tolerant

3.3V LVTTL

HoldPri

Hold Primary. Used by an external master to indicate the

priority of a given transfer (0 = high, 1 = low).

I

5V tolerant

3.3V LVTTL

1, 4

BusReq

Bus Request. Used when the NPe405H needs to regain

control of peripheral interface from an external Master.

O

5V tolerant

3.3V LVTTL

Internal Peripheral Interface

UARTSerClk

Serial Clock used to provide an alternative clock to the

internally generated serial clock. Used in cases where the

allowable internally generated baud rates are not

satisfactory. This input can be individually connected to

either or both UART0 and UART1.

I

5V tolerant

3.3V LVTTL

1, 4

UART0_Rx

UART0 Receive data.

I

5V tolerant

3.3V LVTTL

1, 4

UART0_Tx

UART0 Transmit data.

O

5V tolerant

3.3V LVTTL

[UART0_DCD]

UART0 Data Carrier Detect.

I

5V tolerant

3.3V LVTTL

1, 4

[UART0_DSR]

UART0 Data Set Ready.

I

5V tolerant

3.3V LVTTL

1, 4

[UART0_CTS]

UART0 Clear To Send.

I

5V tolerant

3.3V LVTTL

1, 4

[UART0_DTR]

UART0 Data Terminal Ready.

O

5V tolerant

3.3V LVTTL

[UART0_RTS]

UART0 Request To Send.

O

5V tolerant

3.3V LVTTL

[UART0_RI]

UART0 Ring Indicator.

I

5V tolerant

3.3V LVTTL r

1, 4

Signal Functional Description

(Part 7 of 9)

Notes:

1. Receiver input has hysteresis

2. Must pull up (recommended value is 3k

to 3.3V, 10k

to 5V

)

3. Must pull down (recommended value is 1k

)

4. If not used, must pull up (recommended value is 3k

to 3.3V)

5. If not used, must pull down (recommended value is 1k

)

Signal Name

Description

I/O

Type

Notes

相关PDF资料 |

PDF描述 |

|---|---|

| PowerNP NPe405L | 32-Bit Embedded Processor(32位嵌入式处理器) |

| PowerNP NPe405 | 32-Bit Embedded Processor(32位嵌入式处理器(应用于网络方面,提供高性价比)) |

| PowerPC 401GF | 32-bit RISC Embedded Controllers(32位RISC结构嵌入式控制器) |

| PowerPC 403GA | 32-bit RISC Embedded Controllers(32位RISC结构嵌入式控制器) |

| PowerPC 403GB | 32-bit RISC Embedded Controllers(32位RISC结构嵌入式控制器) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| POWERPAC-B | 制造商:IAR Systems 功能描述:PowerPac |

| POWERPAC-S | 制造商:IAR Systems 功能描述:PowerPac |

| POWERPAT PLUS | 制造商:Fluke Electronics 功能描述:SOFTWARE PAT |

| POWERPATPLUS | 制造商:Fluke Electronics 功能描述:Fluke Powerpat Plus |

| POWERPLUG15W | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:AC/DC POWER SUPPLY |

发布紧急采购,3分钟左右您将得到回复。