- 您现在的位置:买卖IC网 > PDF目录370013 > PowerNP NPe405H (IBM Microeletronics) 32-Bit Embedded Processor(32位嵌入式处理器) PDF资料下载

参数资料

| 型号: | PowerNP NPe405H |

| 厂商: | IBM Microeletronics |

| 英文描述: | 32-Bit Embedded Processor(32位嵌入式处理器) |

| 中文描述: | 32位嵌入式处理器(32位嵌入式处理器) |

| 文件页数: | 38/64页 |

| 文件大小: | 1050K |

| 代理商: | POWERNP NPE405H |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页当前第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

Advance Information

PowerNP

TM

NPe405H Embedded Processor Data Sheet

38

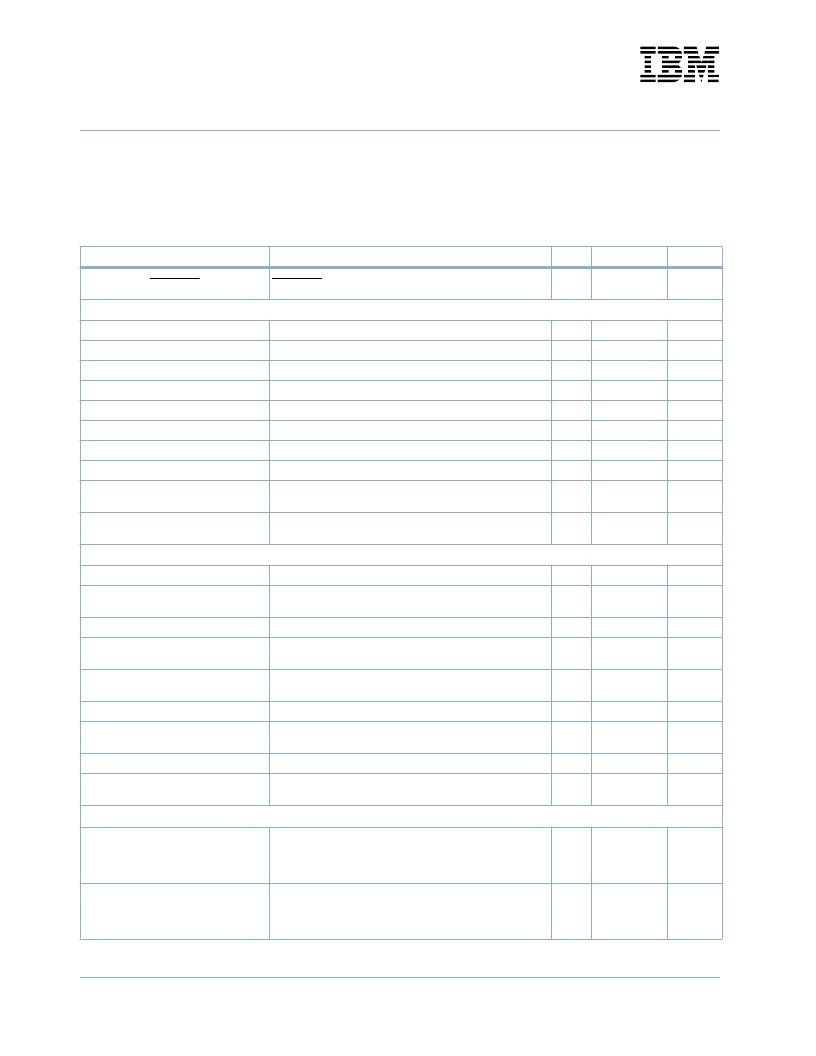

PCIGnt1:5

PCIGnt1:5 output when internal arbiter is used.

O

5V tolerant

3.3V PCI

HDLCEX Interface

HDLCEXTxClk

Transmit Clock

I

3.3V LVTTL

HDLCEXTxFS

Transmit Frame Synchronization

I

3.3V LVTTL

HDLCEXTxDataA

Transmit Data port A

O

3.3V LVTTL

HDLCEXTxDataB

Transmit Data port B

O

3.3V LVTTL

HDLCEXRxClk

Receive Clock

I

3.3V LVTTL

HDLCEXRxFS

Receive Frame Synchronization

I

3.3V LVTTL

HDLCEXRxDataA

Receive Data port A

I

3.3V LVTTL

HDLCEXRxDataB

Receive Data port B

I

3.3V LVTTL

[HDLCEXTxEnA]

Transmit Enable port A

O

5V tolerant

3.3V LVTTL

[HDLCEXTxEnB]

Transmit Enable port B

O

5V tolerant

3.3V LVTTL

HDLCMP Interface

HDLCMPTxClk0:3

Transmit Clock signal that controls the transmit bit rate

O

3.3V LVTTL

[HDLCMPTxClk4:7]

Transmit Clock signal that controls the transmit bit rate

O

5V tolerant

3.3V LVTTL

HDLCMPTxData0:3

Transmit Data signal

O

3.3V LVTTL

[HDLCMPTxData4:7]

Transmit Data signal

O

5V tolerant

3.3V LVTTL

[HDLCMPTxEn0:7]

Transmit Data Enable signal that controls when the

external buffer is tri-stated

O

5V tolerant

3.3V LVTTL

HDLCMPRxClk0:3

Receive Clock signal that controls the receive bit rate

I

3.3V LVTTL

[HDLCMPRxClk4:7]

Receive Clock signal that controls the receive bit rate

I

5V tolerant

3.3V LVTTL

HDLCMPRxData0:3

Receive Data signal

I

3.3V LVTTL

[HDLCMPRxData4:7]

Receive Data signal

I

5V tolerant

3.3V LVTTL

Ethernet Interface

EMC0MDClk

Management Data Clock. The MDClk is sourced to the

PHY. Management information is transferred

synchronously with respect to this clock (MII, RMII, and

SMII).

O

5V tolerant

3.3V LVTTL

EMC0MDIO

Management Data Input/Output is a bidirectional signal

between the Ethernet controller and the PHY. It is used to

transfer control and status information (MII, RMII, and

SMII).

I/O

5V tolerant

3.3V LVTTL

1, 4

Signal Functional Description

(Part 2 of 9)

Notes:

1. Receiver input has hysteresis

2. Must pull up (recommended value is 3k

to 3.3V, 10k

to 5V

)

3. Must pull down (recommended value is 1k

)

4. If not used, must pull up (recommended value is 3k

to 3.3V)

5. If not used, must pull down (recommended value is 1k

)

Signal Name

Description

I/O

Type

Notes

相关PDF资料 |

PDF描述 |

|---|---|

| PowerNP NPe405L | 32-Bit Embedded Processor(32位嵌入式处理器) |

| PowerNP NPe405 | 32-Bit Embedded Processor(32位嵌入式处理器(应用于网络方面,提供高性价比)) |

| PowerPC 401GF | 32-bit RISC Embedded Controllers(32位RISC结构嵌入式控制器) |

| PowerPC 403GA | 32-bit RISC Embedded Controllers(32位RISC结构嵌入式控制器) |

| PowerPC 403GB | 32-bit RISC Embedded Controllers(32位RISC结构嵌入式控制器) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| POWERPAC-B | 制造商:IAR Systems 功能描述:PowerPac |

| POWERPAC-S | 制造商:IAR Systems 功能描述:PowerPac |

| POWERPAT PLUS | 制造商:Fluke Electronics 功能描述:SOFTWARE PAT |

| POWERPATPLUS | 制造商:Fluke Electronics 功能描述:Fluke Powerpat Plus |

| POWERPLUG15W | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:AC/DC POWER SUPPLY |

发布紧急采购,3分钟左右您将得到回复。