- 您现在的位置:买卖IC网 > PDF目录192277 > S-812C52AY-Z-G 5.2 V FIXED POSITIVE LDO REGULATOR, 0.25 V DROPOUT, PBCY3 PDF资料下载

参数资料

| 型号: | S-812C52AY-Z-G |

| 元件分类: | 固定正电压单路输出LDO稳压器 |

| 英文描述: | 5.2 V FIXED POSITIVE LDO REGULATOR, 0.25 V DROPOUT, PBCY3 |

| 封装: | LEAD FREE, TO-92, 3 PIN |

| 文件页数: | 37/39页 |

| 文件大小: | 690K |

| 代理商: | S-812C52AY-Z-G |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页

W946432AD

512K

× 4 BANKS × 32 BITS DDR SDRAM

PRELIMINARY DATA:11/13/01

7

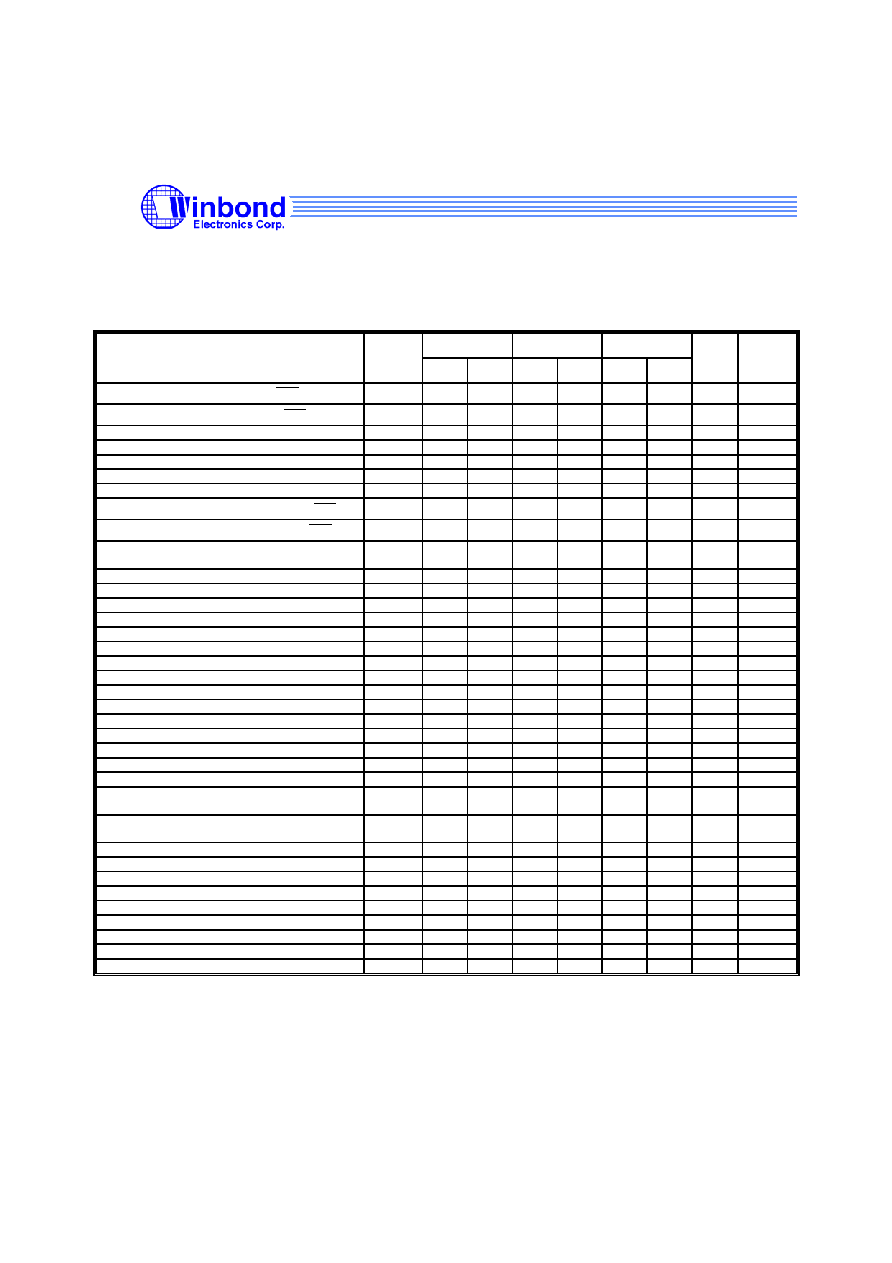

AC CHARACTERISTICS

(0 °C

≤ TA ≤ 70 °C; for –55 / –6 VDD/VDDQ= 2.5V ± 6% for ”-5H” VDD/VDDQ = +2.6V ± 0.1V, VDD = +2.6V ± 0.1V)

PARAMETER

-5H

55

-6

UNIT NOTE

MIN. MAX. MIN. MAX. MIN. MAX.

DQ output access time from CLK/ CLK

tAC

-0.1

0.1

-0.1

0.1

-0.1

0.1

tCK

DQS output access time from CLK/ CLK

tDQSCK

-0.1

0.1

-0.1

0.1

-0.1

0.1

tCK

CLK high-level width

tCH

0.45

0.55

0.45

0.55

0.45

0.55

tCK

CLK low-level width

tCL

0.45

0.55

0.45

0.55

0.45

0.55

tCK

Clock cycle time

tCLK

5

8

5.5

8

6

8

ns

8

DQ and DM input hold time

tDH

1

ns

DQ and DM input setup time

tDS

0.5

ns

Data-out high-impedance time from CLK/ CLK

tHZ

-0.1

0.1

-0.1

0.1

-0.1

0.1

tCK

Data-out low-impedance time from CLK/ CLK

tLZ

-0.1

0.1

-0.1

0.1

-0.1

0.1

tCK

DQS-DQ Skew (for DQS and associated DQ

signals)

tDQSQ

0.5

ns

DQS-DQ Skew (for DQS and all DQ signals)

tDQSQA

0.45

ns

DQ/DQS output valid time

tDV

0.2

tCK

Write command to first DQS latching transition

tDQSS

0.75

1.25

0.75

1.25

0.75

1.25

tCK

DQS input high pulse width

tDQSH

0.4

0.6

0.4

0.6

0.4

0.6

tCK

DQS input low pulse width

tDQSL

0.4

0.6

0.4

0.6

0.4

0.6

tCK

DQS falling edge to CLK setup time

tDSS

0.2

tCK

DQS falling edge hold time from CLK

tDSH

0.2

tCK

MODE REGISTER SET command cycle time

tMRD

2

tCK

Write postamble

tWPST

0.4

0.6

0.4

0.6

0.4

0.6

tCK

Write preamble

tWPRE

0.25

tCK

Address and Control input hold time

tIH

1

ns

Address and Control input setup time

tIS

1

ns

Read preamble

tRPRE

0.9

1.1

0.9

1.1

0.9

1.1

tCK

Read postamble

tRPST

0.4

0.6

0.4

0.6

0.4

0.6

tCK

ACTIVE to PRECHARGE command

tRAS

35

120K

35

120K

42

120K ns

ACTIVE to ACTIVE/Auto Refresh command

period

tRC

55

60.5

60

ns

Auto Refresh to Active/Auto Refresh command

period

tRFC

65

71

72

ns

ACTIVE to READ or WRITE delay

tRCD

15

16.5

18

ns

PRECHARGE command period

tRP

16

16.5

18

ns

ACTIVE bank A to ACTIVE bank B command

tRRD

10

11

12

ns

Write recovery time

tWR

10

11

12

ns

Auto Precharge write recovery + precharge time

tDAL

25

27.5

30

ns

Internal Write to Read Command Delay

tWTR

2

tCK

9

Exit SELF REFRESH to non-READ command

tXSNR

65

71

72

ns

Exit SELF REFRESH to READ command

tXSRD

200

tCK

Average Periodic Refresh Interval

tREFI

15.6

us

相关PDF资料 |

PDF描述 |

|---|---|

| S-812C52BMC-C5GT2G | 5.2 V FIXED POSITIVE LDO REGULATOR, 0.25 V DROPOUT, PDSO5 |

| S-81332HG-KC-S | 3.2 V FIXED POSITIVE REGULATOR, PSSO3 |

| S-81332HG-KC-T1 | 3.2 V FIXED POSITIVE REGULATOR, PSSO3 |

| S-81332HG-KC-T2 | 3.2 V FIXED POSITIVE REGULATOR, PSSO3 |

| S-814A33AUC-BCXT2G | 3.3 V FIXED POSITIVE LDO REGULATOR, 0.44 V DROPOUT, PDSO5 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| S-812C52BMC-C5GT2G | 功能描述:低压差稳压器 - LDO Linear LDO Reg 1.0uA Iq 75mA Iout ON/OFF RoHS:否 制造商:Texas Instruments 最大输入电压:36 V 输出电压:1.4 V to 20.5 V 回动电压(最大值):307 mV 输出电流:1 A 负载调节:0.3 % 输出端数量: 输出类型:Fixed 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-20 |

| S-812C52BMC-C5GT2U | 功能描述:IC REG LINEAR 75MA SOT23-5 制造商:ablic u.s.a. inc. 系列:* 包装:剪切带(CT) 零件状态:在售 稳压器数:1 电流 - 输出:75mA 工作温度:-40°C ~ 85°C(TA) 安装类型:表面贴装 封装/外壳:SC-74A,SOT-753 供应商器件封装:SOT-23-5 标准包装:1 |

| S-812C52BPI-C5GTFG | 功能描述:低压差稳压器 - LDO Linear LDO Reg 1.0uA Iq 75mA Iout ON/OFF RoHS:否 制造商:Texas Instruments 最大输入电压:36 V 输出电压:1.4 V to 20.5 V 回动电压(最大值):307 mV 输出电流:1 A 负载调节:0.3 % 输出端数量: 输出类型:Fixed 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-20 |

| S-812C52BPI-C5GTFU | 功能描述:IC REG LINEAR 75MA SNT6A 制造商:ablic u.s.a. inc. 系列:- 包装:剪切带(CT) 零件状态:在售 输出配置:正 输出类型:固定 稳压器数:1 电压 - 输入(最大值):16V 电压 - 输出(最小值/固定):5.2V 电压 - 输出(最大值):- 压降(最大值):0.25V @ 10mA 电流 - 输出:75mA 电流 - 静态(Iq):2.5μA PSRR:- 控制特性:使能 保护功能:短路 工作温度:-40°C ~ 85°C(TA) 安装类型:表面贴装 封装/外壳:6-SMD,扁平引线 供应商器件封装:SNT-6A(H) 标准包装:1 |

| S-812C53AMC-C3H-T2 | 功能描述:低压差稳压器 - LDO 5.3V 1.0uA 2.0% RoHS:否 制造商:Texas Instruments 最大输入电压:36 V 输出电压:1.4 V to 20.5 V 回动电压(最大值):307 mV 输出电流:1 A 负载调节:0.3 % 输出端数量: 输出类型:Fixed 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-20 |

发布紧急采购,3分钟左右您将得到回复。