- 您现在的位置:买卖IC网 > PDF目录98071 > S80486-DX4-75-S-V-8-B (ADVANCED MICRO DEVICES INC) 32-BIT, 75 MHz, MICROPROCESSOR, PQFP208 PDF资料下载

参数资料

| 型号: | S80486-DX4-75-S-V-8-B |

| 厂商: | ADVANCED MICRO DEVICES INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 75 MHz, MICROPROCESSOR, PQFP208 |

| 封装: | SQFP-208 |

| 文件页数: | 14/69页 |

| 文件大小: | 1070K |

| 代理商: | S80486-DX4-75-S-V-8-B |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页

Enhanced Am486 Microprocessor

AMD

21

PRELIMINARY

If the PWT signal is 0, the external WB/WT signal de-

termines the new state of the line. If the WB/WT signal

was asserted to 1 during reload, the line transits to the

exclusive state. If the WB/WT signal was 0, the line

transits to the shared state. If the PWT signal is 1, it

overrides the WB/WT signal, forcing the line into the

shared state. Therefore, if paging is enabled, the soft-

ware programmed PWT bit can override the hardware

signal WB/WT.

Until the line is reallocated, a write is the only processor

action that can change the state of the line. If the write

occurs to a line in the exclusive state, the data is simply

written into the cache and the line state is changed to

modified. The modified state indicates that the contents

of the line require copy-back to the main memory before

the line is reallocated.

If the write occurs to a line in the shared state, the cache

performs a write of the data on the external bus to up-

date the external memory. The line remains in the

shared state until it is replaced with a new cache line or

until it is flushed. In the modified state, the processor

continues to write the line without any further external

actions or state transitions.

If the PWT or PCD bits are changed for a specified mem-

ory location, the tag bits in the cache are assumed to

be correct. To avoid memory inconsistencies with re-

spect to cacheability and write status, a cache copy-

back and invalidation should be invoked either by using

the WBINVD instruction or asserting the FLUSH signal.

4.8.2

Snooping Actions and State Transitions

To maintain cache coherency, the CPU must allow

snooping by the current bus master. The bus master

initiates a snoop cycle to check whether an address is

cached in the internal cache of the microprocessor. A

snoop cycle differs from any other cycle in that it is ini-

tiated externally to the microprocessor, and the signal

for beginning the cycle is EADS instead of ADS. The

address bus of the microprocessor is bidirectional to

allow the address of the snoop to be driven by the sys-

tem. A snoop access can begin during any hold state:

n while HOLD and HLDA are asserted

n while BOFF is asserted

n while AHOLD is asserted

In the clock in which EADS is asserted, the microprocessor

samples the INV input to qualify the type of inquiry. INV spec-

ifies whether the line (if found) must be invalidated (i.e.,

the MESI status changes to Invalid or ‘I’). A line is inval-

idated if the snoop access was generated due to a write

of another bus master. This is indicated by INV set to 1.

In the case of a read, the line does not have to be inval-

idated, which is indicated by INV set to 0.

The core system logic can generate EADS by watching

the ADS from the current bus master, and INV by watching

the W/R signal. The microprocessor compares the ad-

dress of the snoop request with addresses of lines in

the cache and of any line in the copy-back buffer waiting

to be transferred on the bus. It does not, however, com-

pare with the address of write-miss data in the write

buffers. Two clock cycles after sampling EADS, the mi-

croprocessor drives the results of the snoop on the HITM pin.

If HITM is active, the line was found in the modified state;

if inactive, the line was in the exclusive or shared state,

or was not found.

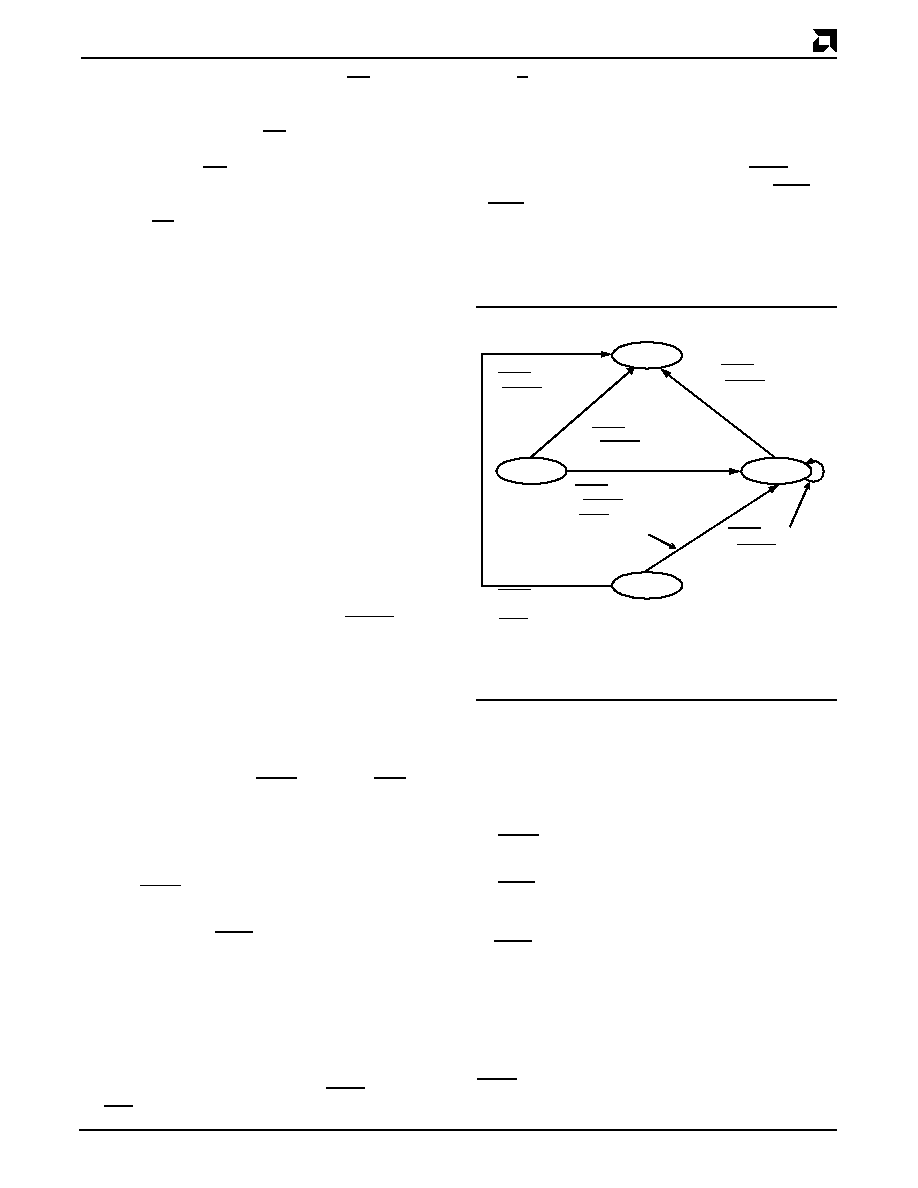

Figure 2 shows a diagram of the state transitions in-

duced by snooping accesses.

4.8.2.1

Difference between Snooping

Access Cases

Snooping accesses are external accesses to the micro-

processor. As described earlier, the snooping logic has

a set of signals independent from the processor-related

signals. Those signals are:

n EADS

n INV

n HITM

In addition to these signals, the address bus is required

as an input. This is achieved by setting AHOLD, HOLD,

or BOFF active.

Snooping can occur in parallel with a processor-initiated

access that has already been started. The two accesses

depend on each other only when a modified line is writ-

ten back. In this case, the snoop requires the use of the

cycle control signals and the data bus. The following sec-

tions describe the scenarios for the HOLD, AHOLD, and

BOFF implementations.

Figure 2. Snooping State Transitions

Invalid

Modified

Exclusive

Shared

(HITM asserted

+ write-back)

(EADS = 0 * INV = 1)

+ FLUSH = 0

(EADS = 0 * INV = 1)

+ FLUSH = 0

EADS = 0 * INV = 0

* FLUSH = 1

EADS = 0 * INV = 0

* FLUSH = 1

(HITM asserted

+ write-back)

EADS = 0 * INV = 0

* FLUSH = 1

EADS = 0 * INV = 1

+ FLUSH = 0

相关PDF资料 |

PDF描述 |

|---|---|

| S80960SA-16 | 32-BIT, 16 MHz, RISC PROCESSOR, PQFP80 |

| S80960SB-10 | 32-BIT, 10 MHz, RISC PROCESSOR, PQFP80 |

| S80C186XL12 | 16-BIT, 12 MHz, MICROPROCESSOR, PQFP80 |

| S80C186XL25 | 16-BIT, 25 MHz, MICROPROCESSOR, PQFP80 |

| S80C186XL20 | 16-BIT, 20 MHz, MICROPROCESSOR, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| S8049CR4 WAF | 制造商:Intel 功能描述: |

| S8049CRA4 WAF | 制造商:Intel 功能描述: |

| S804PV-M63 | 制造商:ABB Control 功能描述:S 800 PV-M 4pole 63A (1200V dc) MCB |

| S804PV-S10 | 制造商:ABB Control 功能描述:MCB S 800 PV-S 4 POLE 10A (800VDC) 制造商:ABB Control 功能描述:MCB, S 800 PV-S 4 POLE 10A (800VDC) |

| S804PV-S16 | 制造商:ABB Control 功能描述:MCB S 800 PV-S 4 POLE 16A (800VDC) 制造商:ABB Control 功能描述:MCB, S 800 PV-S 4 POLE 16A (800VDC) |

发布紧急采购,3分钟左右您将得到回复。