- 您现在的位置:买卖IC网 > PDF目录98071 > S80486-DX4-75-S-V-8-B (ADVANCED MICRO DEVICES INC) 32-BIT, 75 MHz, MICROPROCESSOR, PQFP208 PDF资料下载

参数资料

| 型号: | S80486-DX4-75-S-V-8-B |

| 厂商: | ADVANCED MICRO DEVICES INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 75 MHz, MICROPROCESSOR, PQFP208 |

| 封装: | SQFP-208 |

| 文件页数: | 6/69页 |

| 文件大小: | 1070K |

| 代理商: | S80486-DX4-75-S-V-8-B |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页

Enhanced Am486 Microprocessor

AMD

14

PRELIMINARY

BS8/BS16

Bus Size 8 (Active Low; Input)/

Bus Size 16 (Active Low; Input)

The BS8 and BS16 signals allow the processor to op-

erate with 8-bit and 16-bit I/O devices by running multi-

ple bus cycles to respond to data requests: four for 8-

bit devices, and two for 16-bit devices. The bus sizing

pins are sampled every clock. The microprocessor sam-

ples the pins every clock before RDY to determine the

appropriate bus size for the requesting device. The sig-

nals are active Low input with internal pull-up resistors,

and must satisfy setup and hold times t14 and t15 for

correct operation. Bus sizing is not permitted during

copy-back or write-back operation. BS8 and BS16 are

ignored during copy-back or write-back cycles.

CACHE – New

Internal Cacheability (Active Low; Output)

In write-through mode, this signal always floats. In write-

back mode for processor-initiated cycles, a Low output

on this pin indicates that the current read cycle is cache-

able, or that the current cycle is a burst write-back or

copy-back cycle. If the CACHE signal is driven High

during a read, the processor will not cache the data even

if the KEN pin signal is asserted. If the processor deter-

mines that the data is cacheable, CACHE goes active

when ADS is asserted and remains in that state until the

next RDY or BRDY is asserted. CACHE floats in re-

sponse to a BOFF or HOLD request.

CLK – Modified

Clock (Input)

The CLK input provides the basic microprocessor timing

signal. The CLKMUL input selects the multiplier value

used to generate the internal operating frequency for

the Enhanced Am486 microprocessor family. All exter-

nal timing parameters are specified with respect to the

rising edge of CLK. The clock signal passes through an

internal Phase-Lock Loop (PLL).

CLKMUL – New

Clock Multiplier (Input)

The microprocessor samples the CLKMUL input signal

at RESET to determine the design operating frequency.

An internal pull-up resistor connects to VCC, which se-

lects clock-tripled mode if the input is High or left floating.

For clock-doubled mode, the input must be pulled Low.

For DX2 versions, this input must always be connected

to VSS to ensure correct operation.

D31–D0

Data Lines (Inputs/Outputs)

Lines D31–D0 define the data bus. The signals must

meet setup and hold times t22 and t23 for proper read op-

erations. These pins are driven during the second and sub-

sequent clocks of write cycles.

D/C

Data/Control (Output)

This bus cycle definition pin distinguishes memory and

I/O data cycles from control cycles. The control cycles

are:

n Interrupt Acknowledge

n Halt/Special Cycle

n Code Read (instruction fetching)

DP3–DP0

Data Parity (Inputs/Outputs)

Data parity is generated on all write data cycles with the

same timing as the data driven by the microprocessor.

Even parity information must be driven back into the

microprocessor on the data parity pins with the same

timing as read information to ensure that the processor

uses the correct parity check. The signals read on these

pins do not affect program execution. Input signals must

meet setup and hold times t

22 and t23. DP3–DP0 should

be connected to V

CC through a pull-up resistor in systems

not using parity. DP3–DP0 are active High and are driven

during the second and subsequent clocks of write cycles.

EADS – Modified

External Address Strobe (Active Low; Input)

This signal indicates that a valid external address has

been driven on the address pins A31–A4 of the micro-

processor to be used for a cache snoop. This signal is

recognized while the processor is in hold (HLDA is driv-

en active), while forced off the bus with the BOFF input,

or while AHOLD is asserted. The microprocessor ig-

nores EADS at all other times. EADS is not recognized

if HITM is active, nor during the clock after ADS, nor

during the clock after a valid assertion of EADS. Snoops

to the on-chip cache must be completed before another

snoop cycle is initiated. Table 2 describes EADS when

first sampled. EADS can be asserted every other clock

cycle as long as the hold remains active and HITM re-

mains inactive. INV is sampled in the same clock period

that EADS is asserted. EADS has an internal weak pull-up.

Note: The triggering signal (AHOLD, HOLD, or BOFF)

must remain active for at least 1 clock after EADS to

ensure proper operation.

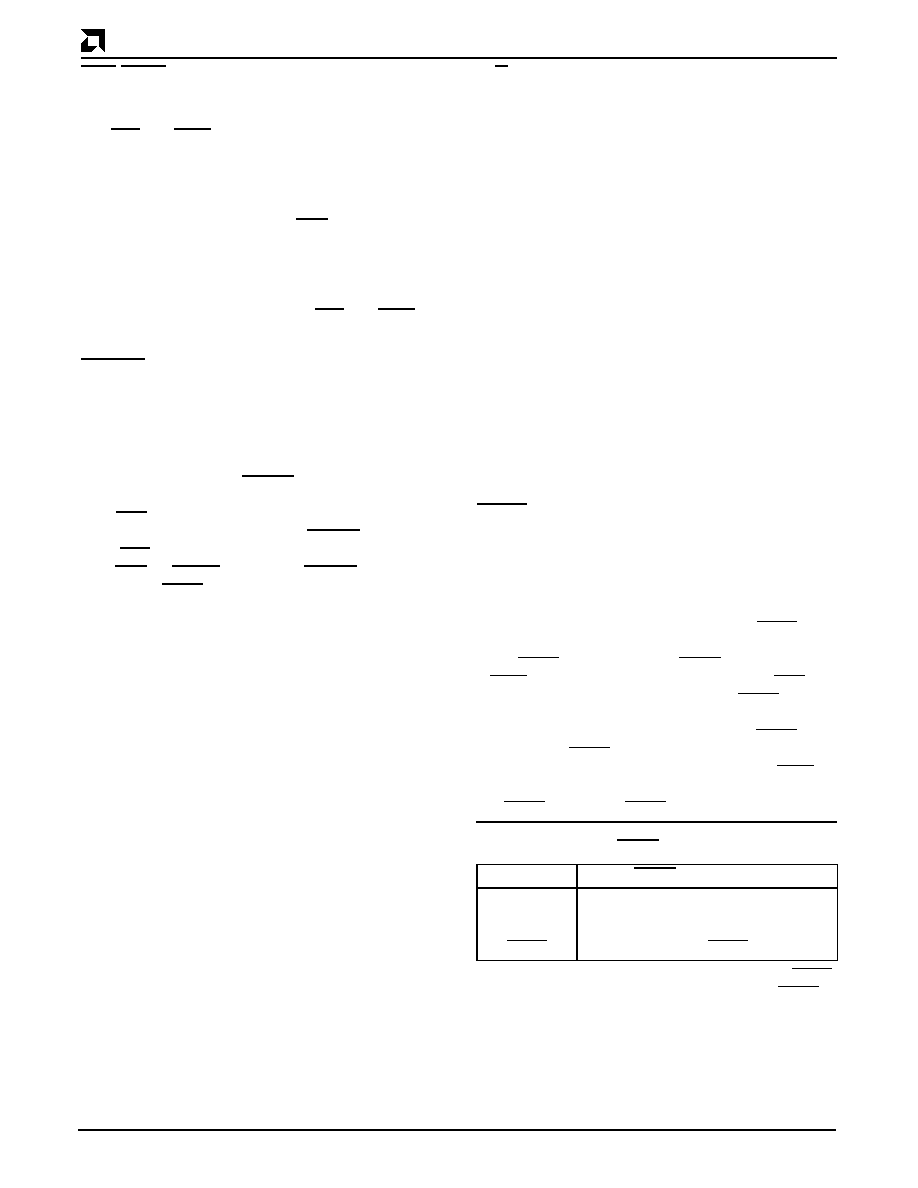

Table 2. EADS Sample Time

Trigger

EADS First Sampled

AHOLD

Second clock after AHOLD asserted

HOLD

First clock after HLDA asserted

BOFF

Second clock after BOFF asserted

相关PDF资料 |

PDF描述 |

|---|---|

| S80960SA-16 | 32-BIT, 16 MHz, RISC PROCESSOR, PQFP80 |

| S80960SB-10 | 32-BIT, 10 MHz, RISC PROCESSOR, PQFP80 |

| S80C186XL12 | 16-BIT, 12 MHz, MICROPROCESSOR, PQFP80 |

| S80C186XL25 | 16-BIT, 25 MHz, MICROPROCESSOR, PQFP80 |

| S80C186XL20 | 16-BIT, 20 MHz, MICROPROCESSOR, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| S8049CR4 WAF | 制造商:Intel 功能描述: |

| S8049CRA4 WAF | 制造商:Intel 功能描述: |

| S804PV-M63 | 制造商:ABB Control 功能描述:S 800 PV-M 4pole 63A (1200V dc) MCB |

| S804PV-S10 | 制造商:ABB Control 功能描述:MCB S 800 PV-S 4 POLE 10A (800VDC) 制造商:ABB Control 功能描述:MCB, S 800 PV-S 4 POLE 10A (800VDC) |

| S804PV-S16 | 制造商:ABB Control 功能描述:MCB S 800 PV-S 4 POLE 16A (800VDC) 制造商:ABB Control 功能描述:MCB, S 800 PV-S 4 POLE 16A (800VDC) |

发布紧急采购,3分钟左右您将得到回复。