- 您现在的位置:买卖IC网 > PDF目录98071 > S80486-DX4-75-S-V-8-B (ADVANCED MICRO DEVICES INC) 32-BIT, 75 MHz, MICROPROCESSOR, PQFP208 PDF资料下载

参数资料

| 型号: | S80486-DX4-75-S-V-8-B |

| 厂商: | ADVANCED MICRO DEVICES INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 75 MHz, MICROPROCESSOR, PQFP208 |

| 封装: | SQFP-208 |

| 文件页数: | 18/69页 |

| 文件大小: | 1070K |

| 代理商: | S80486-DX4-75-S-V-8-B |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页

AMD

25

PRELIMINARY

Enhanced Am486 Microprocessor

4.8.3

External Bus Master Snooping Actions

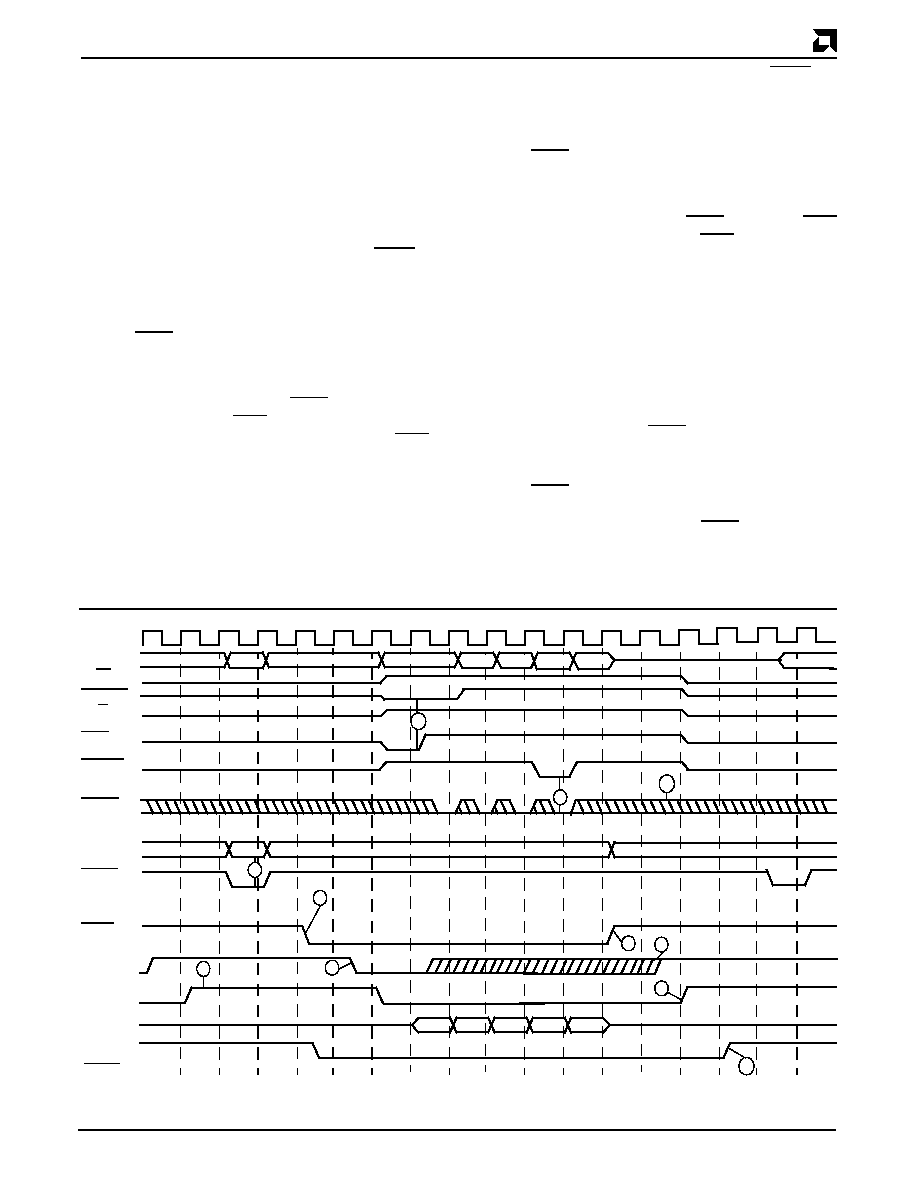

The following scenarios describe the snooping actions

of an external bus master.

4.8.3.1

Snoop Miss

Scenario: A snoop of the on-chip cache does not hit a

line, as shown in Figure 6.

Step 1 The microprocessor is placed in snooping

mode with HOLD. HLDA must be High for a

minimum of one clock cycle before EADS as-

sertion. In the fastest case, this means that

HOLD was asserted one clock cycle before the

HLDA response.

Step 2 EADS and INV are applied to the microprocessor. If

INV is 0, a read access caused the snooping cycle.

If INV is 1, a write access caused the snooping cycle.

Step 3 Two clock cycles after EADS was asserted, the

snooping signal HITM becomes valid. Because the

addressed line is not in the snooping cache, HITM is

1.

4.8.3.2

Snoop Hit to a Non-Modified Line

Scenario: The snoop of the on-chip cache hits a line, and the

line is not modified (see Figure 7).

Step 1 The microprocessor is placed in snooping

mode with HOLD. HLDA must be High for a

minimum of one clock cycle before EADS as-

sertion. In the fastest case, this means that

HOLD was asserted one clock cycle before the

HLDA response.

Step 2 EADS and INV are applied to the microprocessor. If

INV is 0, a read access caused the snooping cycle.

If INV is 1, a write access caused the snooping cycle.

Step 3 Two clock cycles after EADS is asserted, HITM

becomes valid. In this case, HITM is 1.

4.8.4

Write-Back Case

Scenario: Write-back accesses are always burst writes with

a length of four 32-bit words. For burst writes, the burst always

starts with the microprocessor line offset at 0. HOLD must be

deasserted before the write-back can be performed (see Fig-

ure 8).

Step 1 HOLD places the microprocessor in snooping

mode. HLDA must be High for a minimum of one

clock cycle before EADS assertion. In the fastest

case, this means that HOLD asserts one clock cy-

cle before the HLDA response.

Step 2 EADS and INV are asserted. If INV is 0, snooping

is caused by a read access. If INV is 1, snooping is

caused by a write access. EADS is not sampled

again until after the modified line is written back to

memory. It is detected again as early as in Step 11.

EADS

External

bus master’s

BOFF signal

HLDA

Data

HOLD

HITM

ADS

INV

BRDY

BLAST

W/R

M/IO

ADR

CLK

valid

n

n+4

n+8

n+12

n+1

valid

n

Figure 8. Snoop That Hits a Modified Line (Write-Back)

Note: The circled numbers in this figure represent the steps in section 4.8.4.

2

3

1

7

8

9

10

6

5

11

floating/three-stated

CACHE

floating/three-stated

4

n+8

n+4

相关PDF资料 |

PDF描述 |

|---|---|

| S80960SA-16 | 32-BIT, 16 MHz, RISC PROCESSOR, PQFP80 |

| S80960SB-10 | 32-BIT, 10 MHz, RISC PROCESSOR, PQFP80 |

| S80C186XL12 | 16-BIT, 12 MHz, MICROPROCESSOR, PQFP80 |

| S80C186XL25 | 16-BIT, 25 MHz, MICROPROCESSOR, PQFP80 |

| S80C186XL20 | 16-BIT, 20 MHz, MICROPROCESSOR, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| S8049CR4 WAF | 制造商:Intel 功能描述: |

| S8049CRA4 WAF | 制造商:Intel 功能描述: |

| S804PV-M63 | 制造商:ABB Control 功能描述:S 800 PV-M 4pole 63A (1200V dc) MCB |

| S804PV-S10 | 制造商:ABB Control 功能描述:MCB S 800 PV-S 4 POLE 10A (800VDC) 制造商:ABB Control 功能描述:MCB, S 800 PV-S 4 POLE 10A (800VDC) |

| S804PV-S16 | 制造商:ABB Control 功能描述:MCB S 800 PV-S 4 POLE 16A (800VDC) 制造商:ABB Control 功能描述:MCB, S 800 PV-S 4 POLE 16A (800VDC) |

发布紧急采购,3分钟左右您将得到回复。