- 您现在的位置:买卖IC网 > PDF目录98079 > SED122ADXA 16 X 60 DOTS DOT MAT LCD DRVR AND DSPL CTLR, UUC165 PDF资料下载

参数资料

| 型号: | SED122ADXA |

| 元件分类: | 显示控制器 |

| 英文描述: | 16 X 60 DOTS DOT MAT LCD DRVR AND DSPL CTLR, UUC165 |

| 封装: | DIE-165 |

| 文件页数: | 4/50页 |

| 文件大小: | 398K |

| 代理商: | SED122ADXA |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页

4–12

EPSON

SED1220

Pin name

I/O

Description

Q’ty

D7 (SI)

I

8-bit input data bus. These pins are connected to a 8-bit or 16-bit

8

D6 (SCL)

standard MPU data bus.

D5 ~ D0

When P/S = “Low”, the D7 and D6 pins are operated as a serial data

input and a serial clock input respectively.

A0

I

Usually, this pin connects the least significant bit of the MPU address

1

bus and identifies a data command.

0 : Indicates that D0 to D7 are a command.

1 : Indicates that D0 to D7 are display data.

RES

I

In case of a 68 series MPU, initialization can be performed by

1

changing RES

. In case of an 80 series MPU,

initialization can be performed by changing

.

A reset operation is performed by edge sensing of the RES signal.

An interface type for the 68/80 series MPU is selected by input level

after initialization.

“L”

: 68 series MPU interface

“H” : 80 series MPU interface

CS

I

Chip select signal. Usually, this pin inputs the signal obtained by

1

decoding an address bus signal. At the “Low” level, this pin is

enabled.

WR

I

<When connecting an 80 series MPU>

Active “Low”. This pin connects the WR signal of the 80 series

1

(E)

MPU. The signal on the data bus is fetched at the rise of the WR

signal.

<When connecting a 68 series MPU>

Active “High”. This pin becomes an enable clock input of the 68

series MPU.

P/S

I

This pin switches between serial data input and parallel data input.

1

IF

I

Interface data length select pin for parallel data input.

1

“High”: 8-bit parallel input

“Low”: 4-bit parallel input

When P/S = “Low”, connect this pin to VDD or VSS.

CK

I

External input terminal

It must be fixed to “High” when the internal oscillation circuit is used.

1

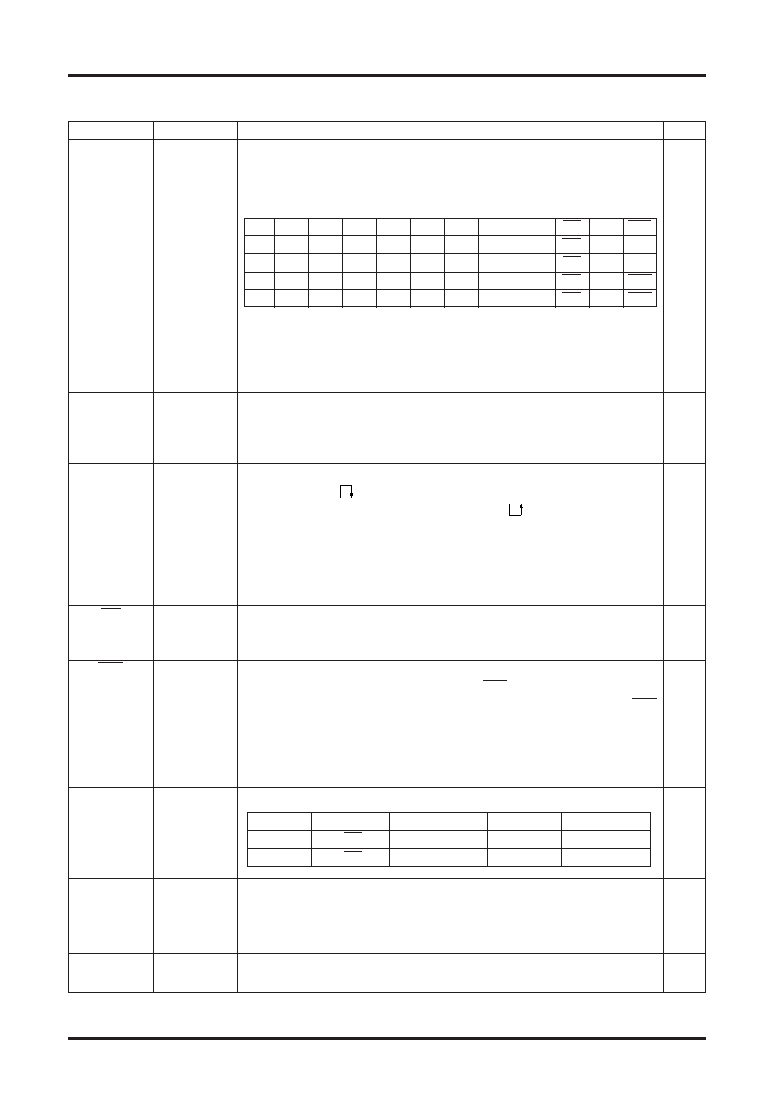

Pins for System Bus Connection

P/S RES I/F

D7

D6

D5

D4

D3-D0

CS

A0

WR

“L”

—

SI

SCL

—

OPEN

CS

A0

—

“H”

D7

D6

D5

D4

D3-D0

CS

A0

E

“H”

“L”

“H”

D7

D6

D5

D4

D3-D0

CS

A0

WR

“H”

“L”

D7

D6

D5

D4

OPEN

CS

A0

WR

P/S

Chip Select Data/Command

Data

Serial Clock

“High”

CS

A0

D0~D7

–

“Low”

CS

A0

SI

SCL

RES: Indicates the active potential.

OPEN:Though “OPEN” is available, fixing the potential is

recommended for noise-withstnading characteristical reason.

—:

Indicates that it can be set at either “H” or “L”, but fixing the

potential is required.

相关PDF资料 |

PDF描述 |

|---|---|

| SED1278FOD | 16 X 40 DOTS DOT MAT LCD DRVR AND DSPL CTLR, PQFP80 |

| SED1278F | 16 X 40 DOTS DOT MAT LCD DSPL CTLR, PQFP80 |

| SED1330FBA | DOT MAT LCD DSPL CTLR, PQFP60 |

| SED1330FBB | 640 X 256 DOTS DOT MAT LCD DSPL CTLR, PQFP60 |

| SED1335FOA | DOT MAT LCD DSPL CTLR, PQFP60 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SED1278 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CMOS DOT MATRIX LCD CONTROLLER DRIVER |

| SED1278D | 制造商:EPSON 制造商全称:EPSON 功能描述:Dot Matrix LCD Controller Driver |

| SED1278D0A | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CMOS DOT MATRIX LCD CONTROLLER DRIVER |

| SED1278D0B | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CMOS DOT MATRIX LCD CONTROLLER DRIVER |

| SED1278D0C | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CMOS DOT MATRIX LCD CONTROLLER DRIVER |

发布紧急采购,3分钟左右您将得到回复。