- 您现在的位置:买卖IC网 > PDF目录98084 > SM320C6201BGLPW20 (TEXAS INSTRUMENTS INC) 32-BIT, 200 MHz, OTHER DSP, CBGA429 PDF资料下载

参数资料

| 型号: | SM320C6201BGLPW20 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 数字信号处理 |

| 英文描述: | 32-BIT, 200 MHz, OTHER DSP, CBGA429 |

| 封装: | CERAMIC, MO-156, BGA-429 |

| 文件页数: | 48/66页 |

| 文件大小: | 971K |

| 代理商: | SM320C6201BGLPW20 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页当前第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页

SM320C6201B, SMJ320C6201B

DIGITAL SIGNAL PROCESSOR

SGUS031B – APRIL 2000 – REVISED AUGUST 2001

52

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251–1443

MULTICHANNEL BUFFERED SERIAL PORT TIMING (CONTINUED)

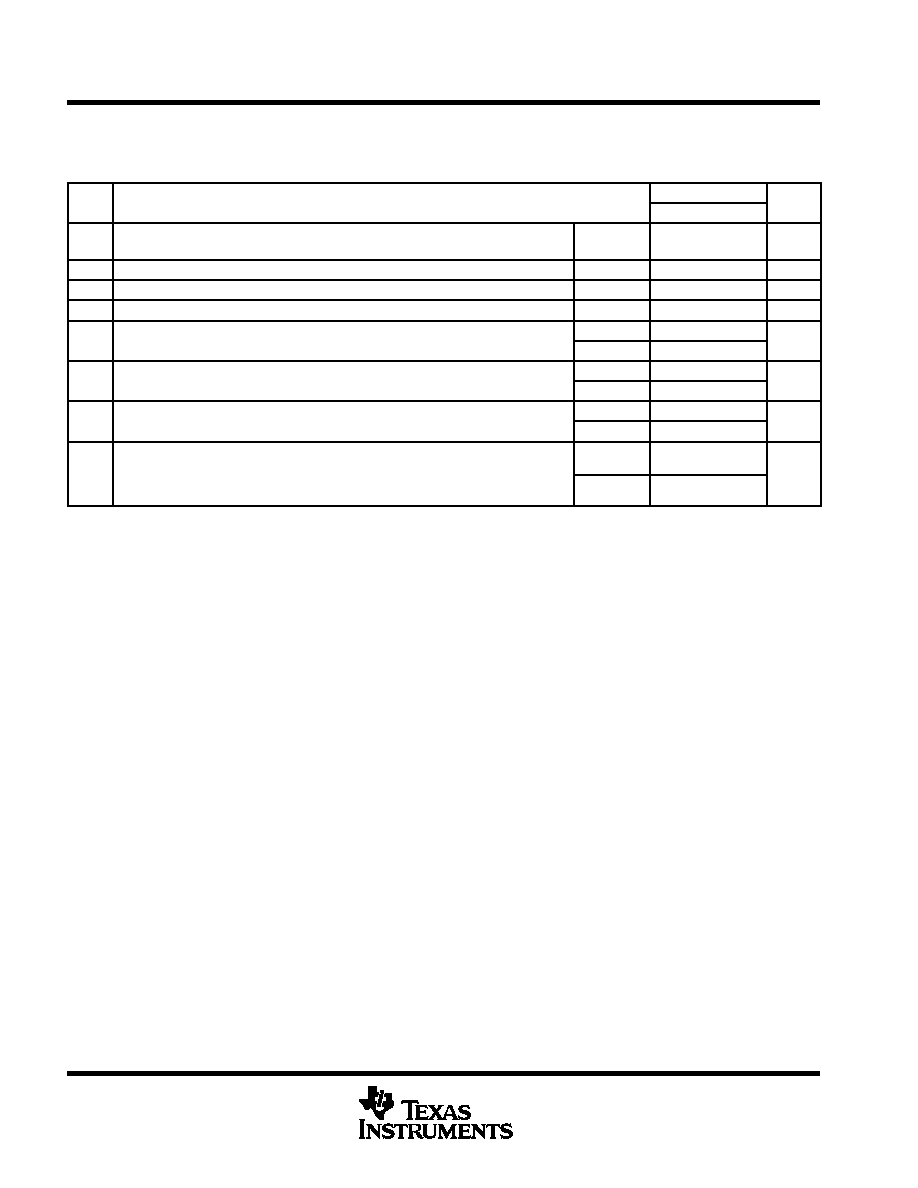

switching characteristics for McBSP§ (see Figure 32)

NO

PARAMETER

C6201B

UNIT

NO.

PARAMETER

MIN

MAX

UNIT

1

td(CKSH-CKRXH)

Delay time, CLKS high to CLKR/X high for internal CLKR/X

generated from CLKS input

3

10

ns

2

tc(CKRX)

Cycle time, CLKR/X

CLKR/X int

2P

ns

3

tw(CKRX)

Pulse duration, CLKR/X high or CLKR/X low

CLKR/X int

*C – 1.6

*C + 1

ns

4

td(CKRH-FRV)

Delay time, CLKR high to internal FSR valid

CLKR int

*–2.5

3

ns

9

t

Dela time CLKX high to internal FSX alid

CLKX int

*–2

3

ns

9

td(CKXH-FXV)

Delay time, CLKX high to internal FSX valid

CLKX ext

*3

*9

ns

12

t

Disable time, DX high impedance following last data bit from

CLKX int

*–1

*4

ns

12

tdis(CKXH-DXHZ)

Disable time, DX high im edance following last data bit from

CLKX high

CLKX ext

*3

*9

ns

13

t

Dela time CLKX high to DX alid

CLKX int

*–1

*4

ns

13

td(CKXH-DXV)

Delay time, CLKX high to DX valid

CLKX ext

*3

*9

ns

14

t

Delay time, FSX high to DX valid

FSX int

*–1

*3

ns

14

td(FXH-DXV)

ONLY applies when in data

delay 0 (XDATDLY = 00b) mode

FSX ext

*3

*9

ns

CLKRP = CLKXP = FSRP = FSXP = 0. If polarity of any of the signals is inverted, then the timing references of that signal are also inverted.

Minimum delay times also represent minimum output hold times.

§ P = 1/CPU clock frequency in ns. For example, when running parts at 200 MHz, use P = 5 ns.

*Not production tested.

C = H or L

S =

sample rate generator input clock = P if CLKSM = 1 (P = 1/CPU clock frequency)

=

sample rate generator input clock = P_clks if CLKSM = 0 (P_clks = CLKS period)

H =

CLKX high pulse width = (CLKGDV/2 + 1) * S if CLKGDV is even

= (CLKGDV + 1)/2 * S if CLKGDV is odd or zero

L =

CLKX low pulse width

= (CLKGDV/2) * S if CLKGDV is even

= (CLKGDV + 1)/2 * S if CLKGDV is odd or zero

相关PDF资料 |

PDF描述 |

|---|---|

| SMJ320C6414DGADW60 | 64-BIT, 75 MHz, OTHER DSP, CPGA570 |

| SM320C6414DGADW60 | 64-BIT, 75 MHz, OTHER DSP, CPGA570 |

| SM320C6416DGADW60 | 64-BIT, 75 MHz, OTHER DSP, CPGA570 |

| SMJ320C6701GLPW16 | 32-BIT, 166.66 MHz, OTHER DSP, CBGA429 |

| SMJ34010-50FDM | GRAPHICS PROCESSOR, CQCC68 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SM320C6201BS14 | 制造商:TI 制造商全称:Texas Instruments 功能描述:FLOATING-POINT DIGITAL SIGNAL PROCESSOR |

| SM320C6201BS16 | 制造商:TI 制造商全称:Texas Instruments 功能描述:FLOATING-POINT DIGITAL SIGNAL PROCESSOR |

| SM320C6201BW14 | 制造商:TI 制造商全称:Texas Instruments 功能描述:FLOATING-POINT DIGITAL SIGNAL PROCESSOR |

| SM320C6201BW16 | 制造商:TI 制造商全称:Texas Instruments 功能描述:FLOATING-POINT DIGITAL SIGNAL PROCESSOR |

| SM320C6201-EP | 制造商:TI 制造商全称:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSOR |

发布紧急采购,3分钟左右您将得到回复。