- 您现在的位置:买卖IC网 > PDF目录98084 > SM320C6201BGLPW20 (TEXAS INSTRUMENTS INC) 32-BIT, 200 MHz, OTHER DSP, CBGA429 PDF资料下载

参数资料

| 型号: | SM320C6201BGLPW20 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 数字信号处理 |

| 英文描述: | 32-BIT, 200 MHz, OTHER DSP, CBGA429 |

| 封装: | CERAMIC, MO-156, BGA-429 |

| 文件页数: | 54/66页 |

| 文件大小: | 971K |

| 代理商: | SM320C6201BGLPW20 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页当前第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页

SM320C6201B, SMJ320C6201B

DIGITAL SIGNAL PROCESSOR

SGUS031B – APRIL 2000 – REVISED AUGUST 2001

58

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251–1443

MULTICHANNEL BUFFERED SERIAL PORT TIMING (CONTINUED)

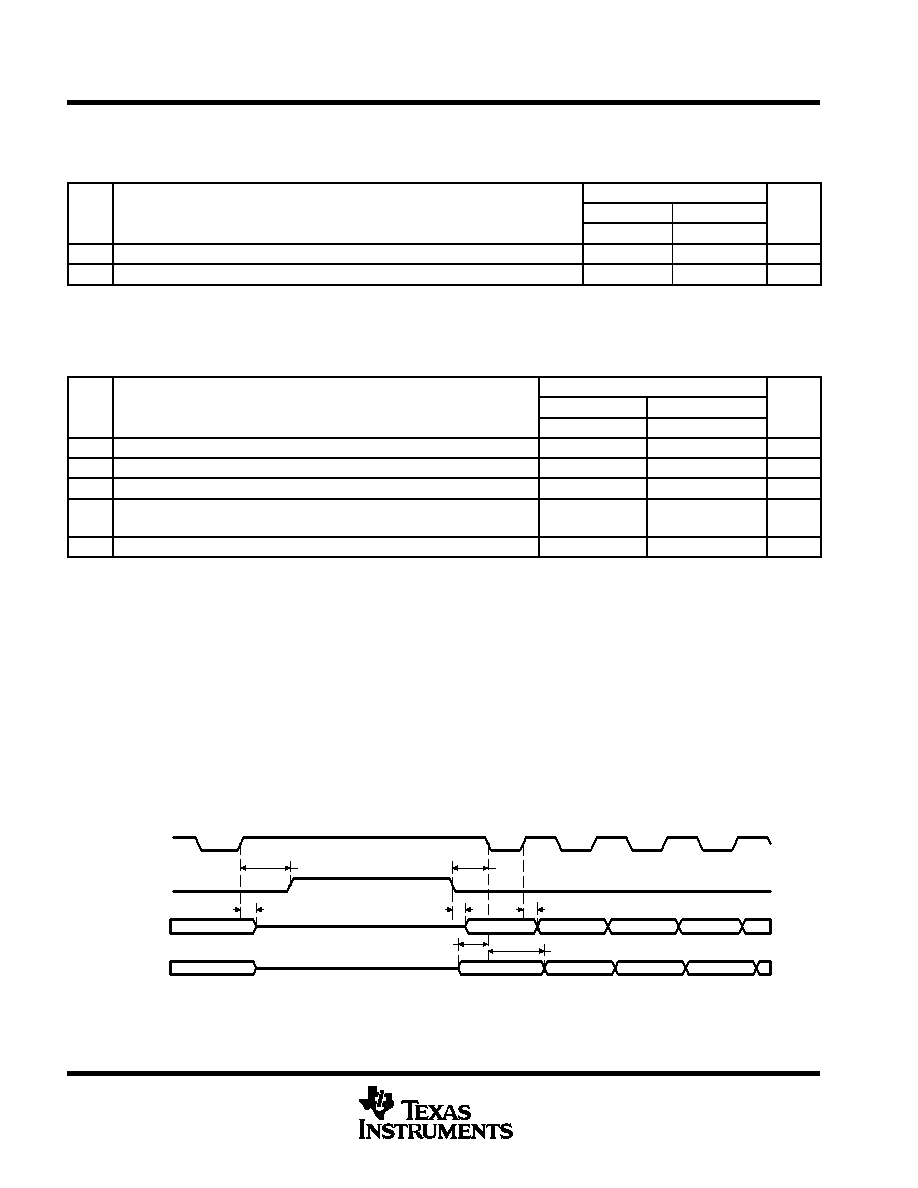

timing requirements for McBSP as SPI master or slave: CLKSTP = 11b, CLKXP = 1 (see Figure 37)

C6201B

NO.

MASTER

SLAVE

UNIT

NO.

MIN

MAX

MIN

MAX

UNIT

4

tsu(DRV-CKXL)

Setup time, DR valid before CLKX low

12

2 – 3P

ns

5

th(CKXL-DRV)

Hold time, DR valid after CLKX low

4

5 + 6P

ns

P = 1/CPU clock frequency in ns. For example, when running parts at 200 MHz, use P = 5 ns.

For all SPI slave modes, CLKG is programmed as 1/2 of the CPU clock by setting CLKSM = CLKGDV = 1.

switching characteristics for McBSP as SPI master or slave: CLKSTP = 11b, CLKXP = 1

(see Figure 37)

C6201B

NO.

PARAMETER

MASTER§

SLAVE

UNIT

NO.

PARAMETER

MIN

MAX

MIN

MAX

UNIT

1

th(CKXH-FXL)

Hold time, FSX low after CLKX high

H – 2

*H + 3

ns

2

td(FXL-CKXL)

Delay time, FSX low to CLKX low#

*T – 2

T + 1

ns

3

td(CKXH-DXV)

Delay time, CLKX high to DX valid

*–2

4

*3P + 3

5P + 17

ns

6

tdis(CKXH-DXHZ)

Disable time, DX high impedance following last data bit

from CLKX high

*–2

*4

*3P + 3

*5P + 17

ns

7

td(FXL-DXV)

Delay time, FSX low to DX valid

*L – 2

L + 4

*2P + 2

4P + 17

ns

P = 1/CPU clock frequency in ns. For example, when running parts at 200 MHz, use P = 5 ns.

For all SPI slave modes, CLKG is programmed as 1/2 of the CPU clock by setting CLKSM = CLKGDV = 1.

§ S = sample rate generator input clock = P if CLKSM = 1 (P = 1/CPU clock frequency)

=

sample rate generator input clock = P_clks if CLKSM = 0 (P_clks = CLKS period)

T =

CLKX period = (1 + CLKGDV) * S

H =

CLKX high pulse width = (CLKGDV/2 + 1) * S if CLKGDV is even

= (CLKGDV + 1)/2 * S if CLKGDV is odd or zero

L =

CLKX low pulse width

= (CLKGDV/2) * S if CLKGDV is even

= (CLKGDV + 1)/2 * S if CLKGDV is odd or zero

FSRP = FSXP = 1. As a SPI master, FSX is inverted to provide active-low slave-enable output. As a slave, the active-low signal input on FSX

and FSR is inverted before being used internally.

CLKXM = FSXM = 1, CLKRM = FSRM = 0 for master McBSP

CLKXM = CLKRM = FSXM = FSRM = 0 for slave McBSP

*Not production tested.

# FSX should be low before the rising edge of clock to enable slave devices and then begin a SPI transfer at the rising edge of the master clock

(CLKX).

Bit 0

Bit(n-1)

(n-2)

(n-3)

(n-4)

Bit 0

Bit(n-1)

(n-2)

(n-3)

(n-4)

5

4

3

7

6

2

1

CLKX

FSX

DX

DR

Figure 37. McBSP Timing as SPI Master or Slave: CLKSTP = 11b, CLKXP = 1

相关PDF资料 |

PDF描述 |

|---|---|

| SMJ320C6414DGADW60 | 64-BIT, 75 MHz, OTHER DSP, CPGA570 |

| SM320C6414DGADW60 | 64-BIT, 75 MHz, OTHER DSP, CPGA570 |

| SM320C6416DGADW60 | 64-BIT, 75 MHz, OTHER DSP, CPGA570 |

| SMJ320C6701GLPW16 | 32-BIT, 166.66 MHz, OTHER DSP, CBGA429 |

| SMJ34010-50FDM | GRAPHICS PROCESSOR, CQCC68 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SM320C6201BS14 | 制造商:TI 制造商全称:Texas Instruments 功能描述:FLOATING-POINT DIGITAL SIGNAL PROCESSOR |

| SM320C6201BS16 | 制造商:TI 制造商全称:Texas Instruments 功能描述:FLOATING-POINT DIGITAL SIGNAL PROCESSOR |

| SM320C6201BW14 | 制造商:TI 制造商全称:Texas Instruments 功能描述:FLOATING-POINT DIGITAL SIGNAL PROCESSOR |

| SM320C6201BW16 | 制造商:TI 制造商全称:Texas Instruments 功能描述:FLOATING-POINT DIGITAL SIGNAL PROCESSOR |

| SM320C6201-EP | 制造商:TI 制造商全称:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSOR |

发布紧急采购,3分钟左右您将得到回复。