- 您现在的位置:买卖IC网 > PDF目录98083 > SM320VC33HFGM150 (TEXAS INSTRUMENTS INC) 32-BIT, 75 MHz, OTHER DSP, CQFP164 PDF资料下载

参数资料

| 型号: | SM320VC33HFGM150 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 数字信号处理 |

| 英文描述: | 32-BIT, 75 MHz, OTHER DSP, CQFP164 |

| 封装: | NCTB, CERAMIC, MO-113AA, QFP-164 |

| 文件页数: | 32/56页 |

| 文件大小: | 669K |

| 代理商: | SM320VC33HFGM150 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

SM320VC33, SMJ320VC33

DIGITAL SIGNAL PROCESSOR

SGUS034E - FEBRUARY 2001 - REVISED OCTOBER 2002

38

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251-1443

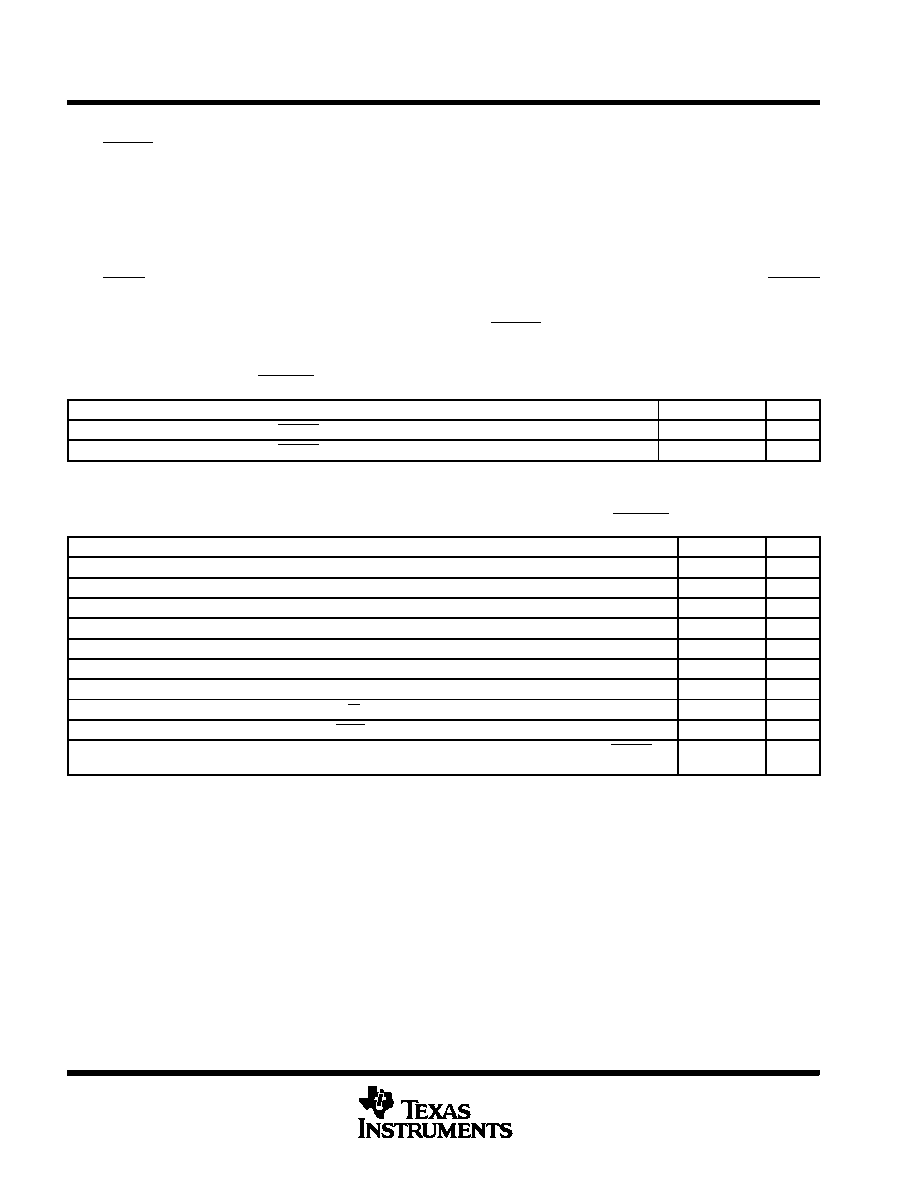

reset timing

RESET is an asynchronous input that can be asserted at any time during a clock cycle. If the specified timings

are met, the exact sequence shown in Figure 27 occurs; otherwise, an additional delay of one clock cycle is

possible.

The asynchronous reset signals include XF0/1, CLKX0, DX0, FSX0, CLKR0, DR0, FSR0, and TCLK0/1.

Resetting the device initializes the bus control register to seven software wait states and therefore results in slow

external accesses until these registers are initialized.

HOLD is a synchronous input that can be asserted during reset. It can take nine CPU cycles before HOLDA

is granted.

The following table defines the timing parameters for the RESET signal. The numbers shown in Figure 27

correspond with those in the NO. column of the following table.

timing requirements for RESET (see Figure 27)

MIN

MAX

UNIT

tsu(RESET-EXTCLKL)

Setup time, RESET before EXTCLK low

5*

P - 7*

ns

tsu(RESETH-H1L)

Setup time, RESET high before H1 low and after ten H1 clock cycles

5

ns

* Not production tested

P = tc(EXTCLK)

switching characteristics over recommended operating conditions for RESET (see Figure 27)

PARAMETER

MIN*

MAX*

UNIT

td(EXTCLKH-H1H)

Delay time, EXTCLK high to H1 high

2

7

ns

td(EXTCLKH-H1L)

Delay time, EXTCLK high to H1 low

2

7

ns

td(EXTCLKH-H3L)

Delay time, EXTCLK high to H3 low

2

7

ns

td(EXTCLKH-H3H)

Delay time, EXTCLK high to H3 high

2

7

ns

tdis(H1H-DZ)

Disable time, Data (high impedance) from H1 high

6

ns

tdis(H3H-AZ)

Disable time, Address (high impedance) from H3 high

6

ns

td(H3H-CONTROLH)

Delay time, H3 high to control signals high

3

ns

td(H1H-RWH)

Delay time, H1 high to R/W high

3

ns

td(H1H-IACKH)

Delay time, H1 high to IACK high

3

ns

tdis(RESETL-ASYNCH)

Disable time, Asynchronous reset signals disabled (high impedance) from RESET

low§

6

ns

* Not production tested

High impedance for Dbus is limited to nominal bus keeper ZOUT = 15 k.

§ Asynchronous reset signals include XF0/1, CLKX0, DX0, FSX0, CLKR0, DR0, FSR0, and TCLK0/1.

相关PDF资料 |

PDF描述 |

|---|---|

| SM34020AHTM32 | GRAPHICS PROCESSOR, CQFP132 |

| SM563 | 4-BIT, MROM, MICROCONTROLLER, PQFP64 |

| SM565 | 4-BIT, MROM, MICROCONTROLLER, PQFP100 |

| SM5K7 | 4-BIT, MROM, MICROCONTROLLER |

| SM5L3 | 4-BIT, MROM, MICROCONTROLLER, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SM320VC33PGEA120EP | 功能描述:数字信号处理器和控制器 - DSP, DSC EP Dig Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| SM320VC5409-EP | 制造商:TI 制造商全称:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSOR |

| SM320VC5409GGU10EP | 功能描述:数字信号处理器和控制器 - DSP, DSC Fxd-pt Dig Sig Proc Mil enhanced RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| SM320VC5416-EP | 制造商:TI 制造商全称:Texas Instruments 功能描述:SM320VC5416-EP Fixed-Point Digital Signal Processor |

| SM320VC5416GGU16EP | 功能描述:数字信号处理器和控制器 - DSP, DSC Fxd-pt Dig Sig Proc Mil enhanced RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。