- 您现在的位置:买卖IC网 > PDF目录4227 > SST25VF064C-80-4C-Q2AE-T (Microchip Technology)IC FLASH SER 64M DUAL I/O 8WSON PDF资料下载

参数资料

| 型号: | SST25VF064C-80-4C-Q2AE-T |

| 厂商: | Microchip Technology |

| 文件页数: | 12/37页 |

| 文件大小: | 0K |

| 描述: | IC FLASH SER 64M DUAL I/O 8WSON |

| 标准包装: | 2,000 |

| 系列: | SST25 |

| 格式 - 存储器: | 闪存 |

| 存储器类型: | FLASH |

| 存储容量: | 64M(8M x 8) |

| 速度: | 80MHz |

| 接口: | SPI 串行 |

| 电源电压: | 2.7 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-WDFN 裸露焊盘 |

| 供应商设备封装: | 8-WSON |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

�� �

�

�

�64� Mbit� SPI� Serial� Dual� I/O� Flash�

�A� Microchip� Technology� Company�

�2.�

�3.�

�4.�

�5.�

�6.�

�7.�

�8.�

�SST25VF064C�

�Data� Sheet�

�Address� bits� above� the� most� significant� bit� can� be� either� V� IL� or� V� IH� .�

�One� bus� cycle� is� four� clock� periods� (dual� operation)�

�4KByte� Sector� Erase� addresses:� use� A� MS� -A� 12,� remaining� addresses� are� don’t� care� but� must� be� set� either� at� V� IL� or� V� IH.�

�32KByte� Block� Erase� addresses:� use� A� MS� -A� 15,� remaining� addresses� are� don’t� care� but� must� be� set� either� at� V� IL� or� V� IH.�

�64KByte� Block� Erase� addresses:� use� A� MS� -A� 16,� remaining� addresses� are� don’t� care� but� must� be� set� either� at� V� IL� or� V� IH.�

�The� Read-Status-Register� is� continuous� with� ongoing� clock� cycles� until� terminated� by� a� low� to� high� transition� on� CE#.�

�Manufacturer’s� ID� is� read� with� A� 0� =� 0,� and� Device� ID� is� read� with� A� 0� =� 1.� All� other� address� bits� are� 00H.� The� Manufac-�

�turer’s� ID� and� device� ID� output� stream� is� continuous� until� terminated� by� a� low-to-high� transition� on� CE#.�

�9.� Requires� a� prior� WREN� command.�

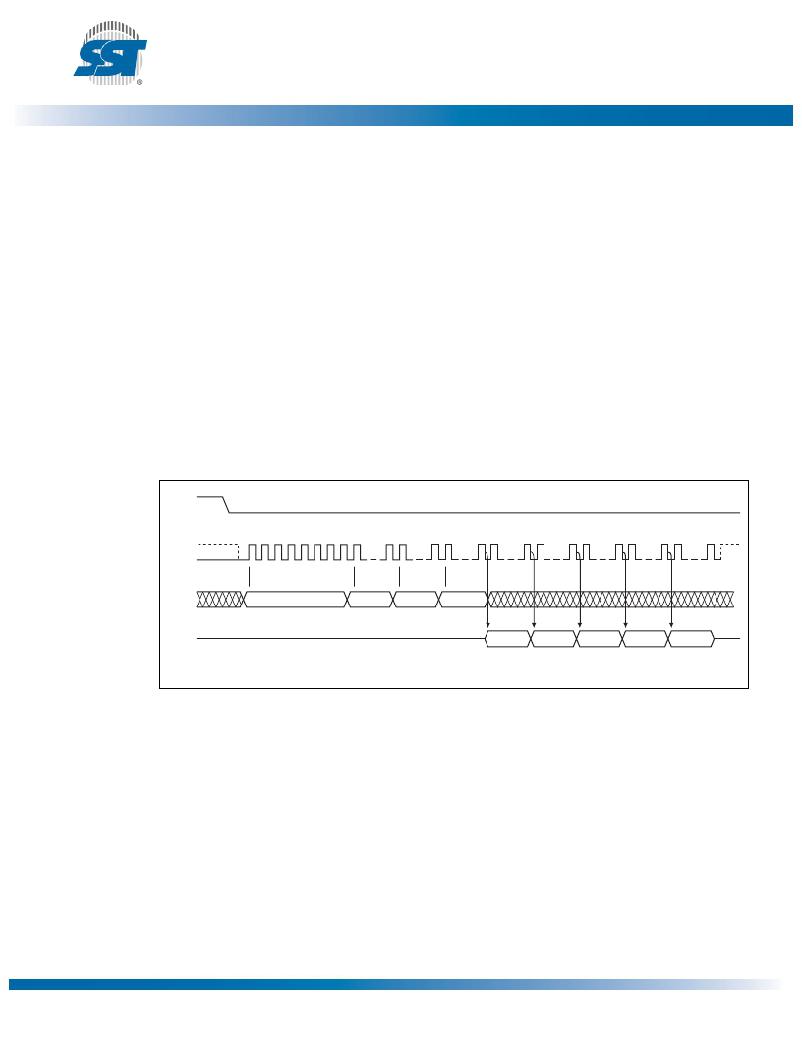

�Read� (33� MHz)�

�The� Read� instruction,� 03H,� supports� up� to� 33� MHz� Read.� The� device� outputs� the� data� starting� from� the�

�specified� address� location.� The� data� output� stream� is� continuous� through� all� addresses� until� termi-�

�nated� by� a� low� to� high� transition� on� CE#.� The� internal� address� pointer� will� automatically� increment� until�

�the� highest� memory� address� is� reached.� Once� the� highest� memory� address� is� reached,� the� address�

�pointer� will� automatically� increment� to� the� beginning� (wrap-around)� of� the� address� space.� For� example,�

�once� the� data� from� address� location� 7FFFFFH� has� been� read,� the� next� output� will� be� from� address�

�location� 000000H.�

�The� Read� instruction� is� initiated� by� executing� an� 8-bit� command,� 03H,� followed� by� address� bits� A� 23� -A� 0� .�

�CE#� must� remain� active� low� for� the� duration� of� the� Read� cycle.� See� Figure� 6� for� the� Read� sequence.�

�CE#�

�MODE� 3�

�0� 1� 2� 3� 4� 5� 6� 7� 8�

�15� 16�

�23� 24�

�31� 32�

�39� 40�

�47�

�48�

�55� 56�

�63� 64�

�70�

�SCK�

�MODE� 0�

�SI�

�03�

�ADD.�

�ADD.�

�ADD.�

�SO�

�MSB�

�MSB�

�HIGH� IMPEDANCE�

�N�

�D� OUT�

�N+1�

�D� OUT�

�N+2�

�D� OUT�

�N+3�

�D� OUT�

�N+4�

�D� OUT�

�MSB�

�1392� F06.0�

�Figure� 6:� Read� Sequence�

�?2011� Silicon� Storage� Technology,� Inc.�

�12�

�DS25036A�

�06/11�

�相关PDF资料 |

PDF描述 |

|---|---|

| AMC10DTEH | CONN EDGECARD 20POS .100 EYELET |

| SST25VF064C-80-4C-Q2AE | IC FLASH SER 64M DUAL I/O 8WSON |

| ASC60DRTS | CONN EDGECARD 120PS .100 DIP SLD |

| SST25VF064C-80-4I-SCE-T | IC FLASH SER 64M DUAL I/O 16SOIC |

| XC2V1000-5FG456I | IC FPGA VIRTEX-II 456FGBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SST25VF064C-80-4C-Q2CE | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:64 Mbit SPI Serial Dual I/O Flash |

| SST25VF064C-80-4C-S3AE | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:64 Mbit SPI Serial Dual I/O Flash |

| SST25VF064C-80-4C-S3CE | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:64 Mbit SPI Serial Dual I/O Flash |

| SST25VF064C-80-4C-SAE | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:64 Mbit SPI Serial Dual I/O Flash |

| SST25VF064C-80-4C-SCE | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:64 Mbit SPI Serial Dual I/O Flash |

发布紧急采购,3分钟左右您将得到回复。