- 您现在的位置:买卖IC网 > PDF目录4227 > SST25VF064C-80-4C-Q2AE-T (Microchip Technology)IC FLASH SER 64M DUAL I/O 8WSON PDF资料下载

参数资料

| 型号: | SST25VF064C-80-4C-Q2AE-T |

| 厂商: | Microchip Technology |

| 文件页数: | 23/37页 |

| 文件大小: | 0K |

| 描述: | IC FLASH SER 64M DUAL I/O 8WSON |

| 标准包装: | 2,000 |

| 系列: | SST25 |

| 格式 - 存储器: | 闪存 |

| 存储器类型: | FLASH |

| 存储容量: | 64M(8M x 8) |

| 速度: | 80MHz |

| 接口: | SPI 串行 |

| 电源电压: | 2.7 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-WDFN 裸露焊盘 |

| 供应商设备封装: | 8-WSON |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

�� �

�

�

�64� Mbit� SPI� Serial� Dual� I/O� Flash�

�A� Microchip� Technology� Company�

�SST25VF064C�

�Data� Sheet�

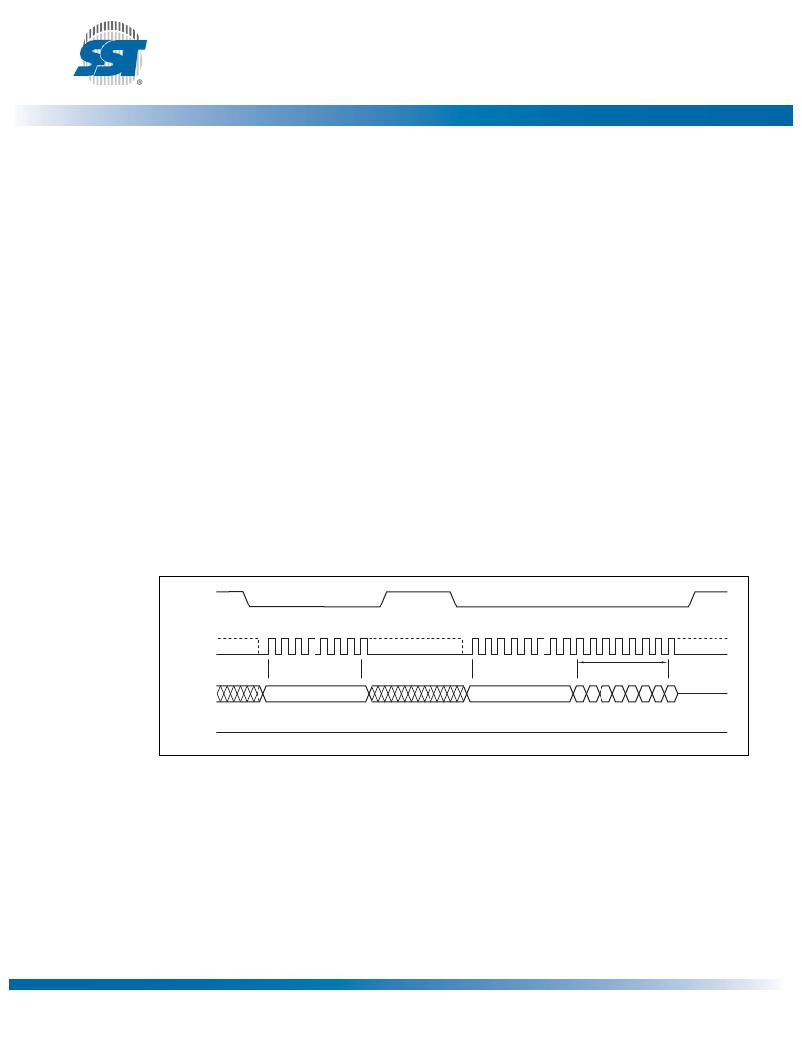

�Enable-Write-Status-Register� (EWSR)�

�The� Enable-Write-Status-Register� (EWSR)� instruction� arms� the� Write-Status-Register� (WRSR)�

�instruction� and� opens� the� status� register� for� alteration.� The� Write-Status-Register� instruction� must� be�

�executed� immediately� after� the� execution� of� the� Enable-Write-Status-Register� instruction.� This� two-�

�step� instruction� sequence� of� the� EWSR� instruction� followed� by� the� WRSR� instruction� works� like� soft-�

�ware� data� protection� (SDP)� command� structure� which� prevents� any� accidental� alteration� of� the� status�

�register� values.� CE#� must� be� driven� low� before� the� EWSR� instruction� is� entered� and� must� be� driven�

�high� before� the� EWSR� instruction� is� executed.�

�Write-Status-Register� (WRSR)�

�The� Write-Status-Register� instruction� writes� new� values� to� the� BP3,� BP2,� BP1,� BP0,� and� BPL� bits� of�

�the� status� register.� CE#� must� be� driven� low� before� the� command� sequence� of� the� WRSR� instruction� is�

�entered� and� driven� high� before� the� WRSR� instruction� is� executed.� See� Figure� 19� for� EWSR� or� WREN�

�and� WRSR� instruction� sequences.�

�Executing� the� Write-Status-Register� instruction� will� be� ignored� when� WP#� is� low� and� BPL� bit� is� set� to�

�‘1’.� When� the� WP#� is� low,� the� BPL� bit� can� only� be� set� from� ‘0’� to� ‘1’� to� lock-down� the� status� register,� but�

�cannot� be� reset� from� ‘1’� to� ‘0’.� When� WP#� is� high,� the� lock-down� function� of� the� BPL� bit� is� disabled� and�

�the� BPL,� BP0,� BP1,� BP2,� and� BP3� bits� in� the� status� register� can� all� be� changed.� As� long� as� BPL� bit� is�

�set� to� ‘0’� or� WP#� pin� is� driven� high� (V� IH� )� prior� to� the� low-to-high� transition� of� the� CE#� pin� at� the� end� of�

�the� WRSR� instruction,� the� bits� in� the� status� register� can� all� be� altered� by� the� WRSR� instruction.� In� this�

�case,� a� single� WRSR� instruction� can� set� the� BPL� bit� to� ‘1’� to� lock� down� the� status� register� as� well� as�

�altering� the� BP0,� BP1,� BP2,� and� BP3� bits� at� the� same� time.� See� Table� 3� for� a� summary� description� of�

�WP#� and� BPL� functions.�

�CE#�

�SCK�

�MODE� 3�

�MODE� 0�

�0� 1� 2� 3� 4� 5� 6� 7�

�MODE� 3�

�MODE� 0�

�0� 1� 2� 3� 4� 5� 6� 7� 8� 9� 10� 11� 12� 13� 14� 15�

�STATUS�

�REGISTER� IN�

�SI�

�SO�

�MSB�

�50� or� 06�

�01�

�MSB�

�HIGH� IMPEDANCE�

�7� 6� 5� 4� 3� 2� 1� 0�

�MSB�

�1392� F20.0�

�Figure� 19:� Enable-Write-Status-Register� (EWSR)� or� Write-Enable� (WREN)� and� Write-Sta-�

�tus-Register� (WRSR)� Sequence�

�?2011� Silicon� Storage� Technology,� Inc.�

�23�

�DS25036A�

�06/11�

�相关PDF资料 |

PDF描述 |

|---|---|

| AMC10DTEH | CONN EDGECARD 20POS .100 EYELET |

| SST25VF064C-80-4C-Q2AE | IC FLASH SER 64M DUAL I/O 8WSON |

| ASC60DRTS | CONN EDGECARD 120PS .100 DIP SLD |

| SST25VF064C-80-4I-SCE-T | IC FLASH SER 64M DUAL I/O 16SOIC |

| XC2V1000-5FG456I | IC FPGA VIRTEX-II 456FGBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SST25VF064C-80-4C-Q2CE | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:64 Mbit SPI Serial Dual I/O Flash |

| SST25VF064C-80-4C-S3AE | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:64 Mbit SPI Serial Dual I/O Flash |

| SST25VF064C-80-4C-S3CE | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:64 Mbit SPI Serial Dual I/O Flash |

| SST25VF064C-80-4C-SAE | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:64 Mbit SPI Serial Dual I/O Flash |

| SST25VF064C-80-4C-SCE | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:64 Mbit SPI Serial Dual I/O Flash |

发布紧急采购,3分钟左右您将得到回复。