- 您现在的位置:买卖IC网 > PDF目录98142 > SST89E554A-40-C-NJ (SILICON STORAGE TECHNOLOGY INC) 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQCC44 PDF资料下载

参数资料

| 型号: | SST89E554A-40-C-NJ |

| 厂商: | SILICON STORAGE TECHNOLOGY INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQCC44 |

| 封装: | PLASTIC, MS-018AC, LCC-44 |

| 文件页数: | 21/87页 |

| 文件大小: | 996K |

| 代理商: | SST89E554A-40-C-NJ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页当前第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页

28

Preliminary Specifications

FlashFlex51 MCU

SST89E554A / SST89V554A

2003 Silicon Storage Technology, Inc.

S71228-00-000

6/03

Symbol

Function

SPIE

If both SPIE and ES are set to one, SPI interrupts are enabled.

SPE

SPI enable bit.

0: Disables SPI.

1: Enables SPI and connects SS#, MOSI, MISO, and SCK to pins P1.4, P1.5, P1.6, P1.7.

DORD

Data Transmission Order.

0: MSB first in data transmission.

1: LSB first in data transmission.

MSTR

Master/Slave select.

0: Selects Slave mode.

1: Selects Master mode.

CPOL

Clock Polarity

0: SCK is low when idle (Active High).

1: SCK is high when idle (Active Low).

CPHA

Clock Phase control bit.

0: Shift triggered on the leading edge of the clock.

1: Shift triggered on the trailing edge of the clock.

SPR1, SPR0

SPI Clock Rate Select bits. These two bits control the SCK rate of the device

configured as master. SPR1 and SPR0 have no effect on the slave. The relationship

between SCK and the oscillator frequency, fOSC, is as follows:

Symbol

Function

SPIF

SPI Interrupt Flag.

Upon completion of data transfer, this bit is set to 1.

If SPIE =1 and ES =1, an interrupt is then generated.

This bit is cleared by software.

WCOL

Write Collision Flag.

Set if the SPI data register is written to during data transfer.

This bit is cleared by software.

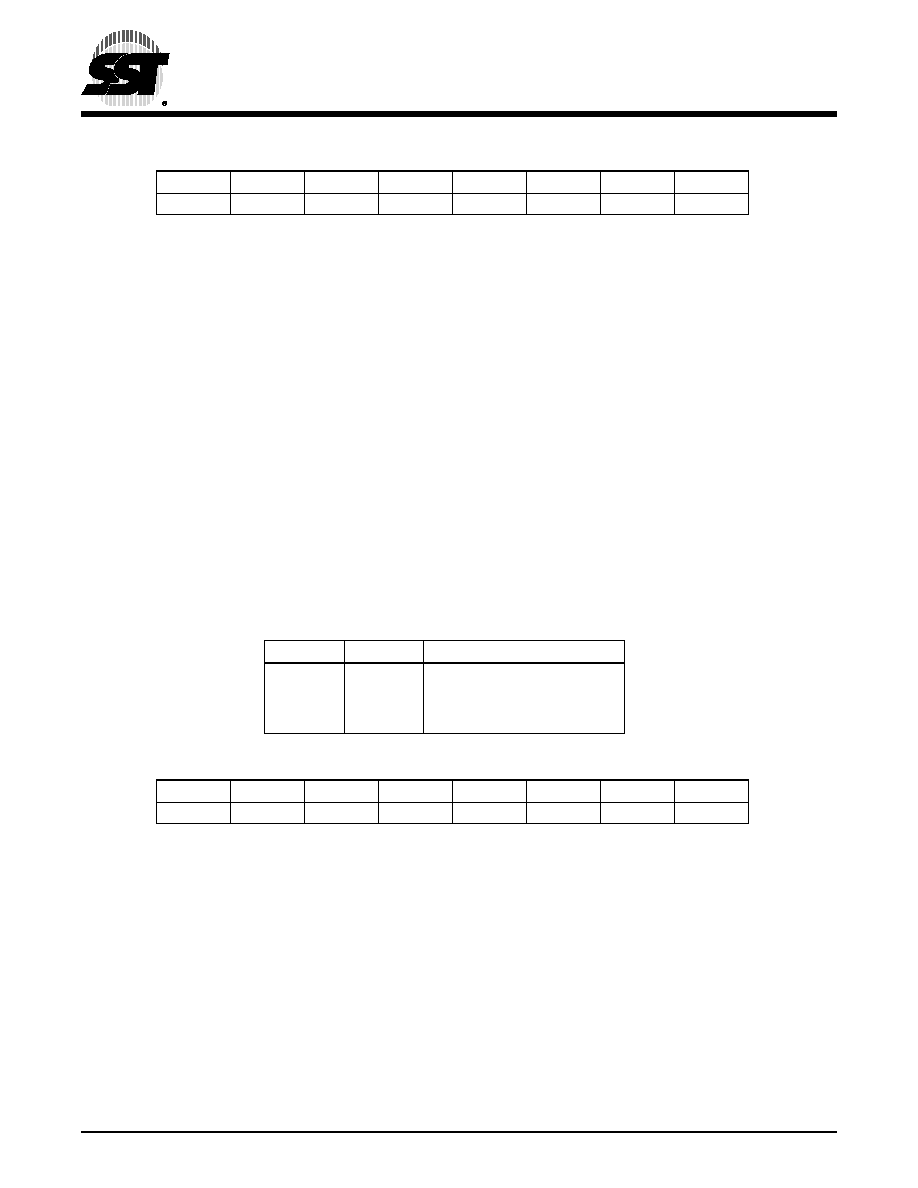

SPI Control Register (SPCR)

Location

76543210

Reset Value

D5H

SPIE

SPE

DORD

MSTR

CPOL

CPHA

SPR1

SPR0

00H

SPR1

SPR0

SCK = fOSC divided by

0

1

0

1

0

1

4

16

64

128

SPI Status Register (SPSR)

Location

76543210

Reset Value

AAH

SPIF

WCOL

------

00xxxxxxb

相关PDF资料 |

PDF描述 |

|---|---|

| SST89E554A-40-I-TQJ | 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQFP44 |

| SSTE32882HLBAKG | SSTE SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA176 |

| SSTE32882HLBBKG | SSTE SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA176 |

| SSTUA32864EC,557 | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| SSTUA32866EC/G | 32866 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PBGA96 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SST89E554RC | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89E554RC-25-C-NI | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89E554RC-25-C-NJ | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89E554RC-25-C-PI | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89E554RC-25-C-PJ | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

发布紧急采购,3分钟左右您将得到回复。