- 您现在的位置:买卖IC网 > PDF目录98142 > SST89E554A-40-C-NJ (SILICON STORAGE TECHNOLOGY INC) 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQCC44 PDF资料下载

参数资料

| 型号: | SST89E554A-40-C-NJ |

| 厂商: | SILICON STORAGE TECHNOLOGY INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQCC44 |

| 封装: | PLASTIC, MS-018AC, LCC-44 |

| 文件页数: | 5/87页 |

| 文件大小: | 996K |

| 代理商: | SST89E554A-40-C-NJ |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页

Preliminary Specifications

FlashFlex51 MCU

SST89E554A / SST89V554A

13

2003 Silicon Storage Technology, Inc.

S71228-00-000

6/03

3.4 Expanded Data RAM Addressing

The SST89E/V554A both have the capability of 1K of

RAM. See Figure 3-2.

The device has four sections of internal data memory:

1. The lower 128 Bytes of RAM (00H to 7FH) are

directly and indirectly addressable.

2. The higher 128 Bytes of RAM (80H to FFH) are

indirectly addressable.

3. The special function registers (80H to FFH) are

directly addressable only.

4. The expanded RAM of 768 Bytes (00H to 2FFH) is

indirectly addressable by the move external

instruction (MOVX) and clearing the EXTRAM bit.

Since the upper 128 bytes occupy the same addresses as

the SFRs, the RAM must be accessed indirectly. The RAM

and SFRs space are physically separate even though they

have the same addresses.

When instructions access addresses in the upper 128

bytes (above 7FH), the MCU determines whether to

access the SFRs or RAM by the type of instruction given. If

it is indirect, then RAM is accessed. If it is direct, then an

SFR is accessed. See the examples below.

Indirect Access:

MOV@R0, #data; R0 contains 90H

Register R0 points to 90H which is located in the upper

address range. Data in “#data” is written to RAM location

90H rather than port 1.

Direct Access:

MOV90H, #data; write data to P1

Data in “#data” is written to port 1. Instructions that write

directly to the address write to the SFRs.

To access the expanded RAM, the EXTRAM bit must be

cleared and MOVX instructions must be used. The extra

768 bytes of memory is physically located on the chip and

logically occupies the first 768 bytes of external memory

(addresses 000H to 2FFH).

When EXTRAM = 0, the expanded RAM is indirectly

addressed using the MOVX instruction in combination

with any of the registers R0, R1 of the selected bank or

DPTR. Accessing the expanded RAM does not affect

ports P0, P3.6 (WR#), P3.7 (RD#), or P2. With

EXTRAM = 0, the expanded RAM can be accessed as

in the following example.

Expanded RAM Access (Indirect Addressing only):

MOVX@DPTR, A; DPTR contains 0A0H

DPTR points to 0A0H and data in “A” is written to address

0A0H of the expanded RAM rather than external memory.

Access to external memory higher than 2FFH using the

MOVX instruction will access external memory (0300H to

FFFFH) and will perform in the same way as the standard

8051, with P0 and P2 as data/address bus, and P3.6 and

P3.7 as write and read timing signals.

When EXTRAM = 1, MOVX @Ri and MOVX @DPTR will

be similar to the standard 8051. Using MOVX @Ri pro-

vides an 8-bit address with multiplexed data on Port 0.

Other output port pins can be used to output higher order

address bits. This provides external paging capabilities.

Using MOVX @DPTR generates a 16-bit address. This

allows external addressing up the 64K. Port 2 provides the

high-order eight address bits (DPH), and Port 0 multiplexes

the low order eight address bits (DPL) with data. Both

MOVX @Ri and MOVX @DPTR generates the necessary

read and write signals (P3.6 - WR# and P3.7 - RD#) for

external memory use. Table 3-3 shows external data mem-

ory RD#, WR# operation with EXTRAM bit.

The stack pointer (SP) can be located anywhere within the

256 bytes of internal RAM (lower 128 bytes and upper 128

bytes). The stack pointer may not be located in any part of

the expanded RAM.

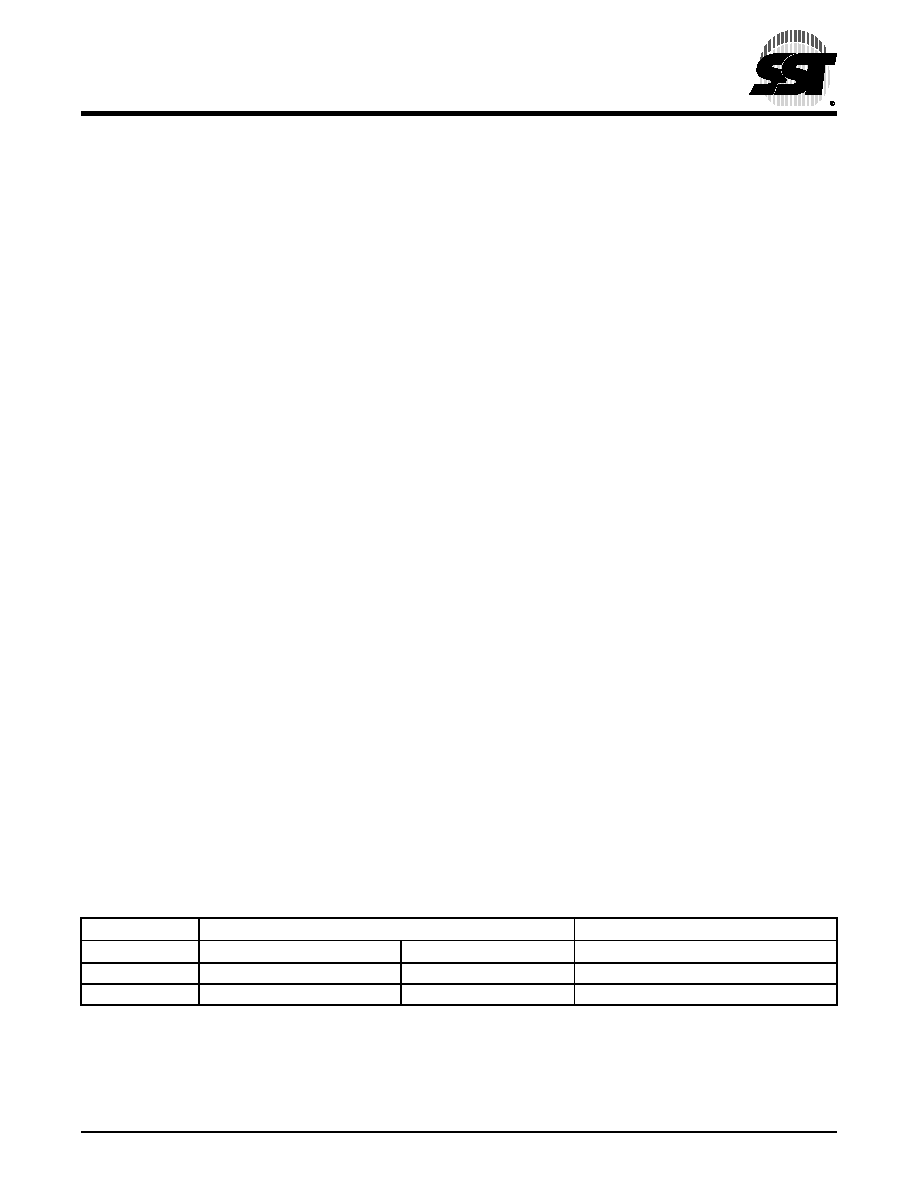

TABLE

3-3: EXTERNAL DATA MEMORY RD#, WR# WITH EXTRAM BIT

MOVX @DPTR, A or MOVX A, @DPTR

MOVX @Ri, A or MOVX A, @Ri

AUXR

ADDR < 0300H

ADDR >= 0300H

ADDR = Any

EXTRAM = 0

RD# / WR# not asserted

RD# / WR# asserted

RD# / WR# not asserted1

1. Access limited to ERAM address within 0 to 0FFH; cannot access 100H to 02FFH.

EXTRAM = 1

RD# / WR# asserted

T3-3.0 1228

相关PDF资料 |

PDF描述 |

|---|---|

| SST89E554A-40-I-TQJ | 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQFP44 |

| SSTE32882HLBAKG | SSTE SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA176 |

| SSTE32882HLBBKG | SSTE SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA176 |

| SSTUA32864EC,557 | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| SSTUA32866EC/G | 32866 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PBGA96 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SST89E554RC | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89E554RC-25-C-NI | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89E554RC-25-C-NJ | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89E554RC-25-C-PI | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89E554RC-25-C-PJ | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

发布紧急采购,3分钟左右您将得到回复。