- 您现在的位置:买卖IC网 > PDF目录98142 > SST89E554A-40-C-NJ (SILICON STORAGE TECHNOLOGY INC) 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQCC44 PDF资料下载

参数资料

| 型号: | SST89E554A-40-C-NJ |

| 厂商: | SILICON STORAGE TECHNOLOGY INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQCC44 |

| 封装: | PLASTIC, MS-018AC, LCC-44 |

| 文件页数: | 31/87页 |

| 文件大小: | 996K |

| 代理商: | SST89E554A-40-C-NJ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页当前第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页

Preliminary Specifications

FlashFlex51 MCU

SST89E554A / SST89V554A

37

2003 Silicon Storage Technology, Inc.

S71228-00-000

6/03

X = Don’t care

4.2 In-Application Programming Mode

The device offers either 40 KByte of in-application pro-

grammable flash memory. During in-application program-

ming, the CPU of the microcontroller enters IAP mode. The

two blocks of flash memory allow the CPU to execute user

code from one block, while the other is being erased or

reprogrammed concurrently. The CPU may also fetch code

from an external memory while all internal flash is being

reprogrammed. The mailbox registers (SFST, SFCM,

SFAL, SFAH, SFDT and SFCF) located in the special func-

tion register (SFR), control and monitor the device’s erase

and program process.

Table 4-4 outlines the commands and their associated

mailbox register settings.

4.2.1 In-Application Programming Mode Clock

Source

During IAP mode, both the CPU core and the flash control-

ler unit are driven off the external clock. However, an inter-

nal oscillator will provide timing references for Program and

Erase operations. The internal oscillator is only turned on

when required, and is turned off as soon as the flash oper-

ation is completed.

4.2.2 Memory Bank Selection for In-Application

Programming Mode

With the addressing range limited to 16 bit, only 64 KByte

of program address space is “visible” at any one time. The

bank selection (the configuration of EA# and SFCF[1:0]),

allows Block 1 memory to be overlaid on the lowest 8

KByte of Block 0 memory, making Block 1 reachable. The

same concept is employed to allow both Block 0 and Block

1 flash to be accessible to IAP operations. Code from a

block that is not visible may not be used as a source to pro-

gram another address. However, a block that is not “visible”

may be programmed by code from the other block through

mailbox registers.

The device allows IAP code in one block of memory to pro-

gram the other block of memory, but may not program any

location in the same block. If an IAP operation originates

physically from Block 0, the target of this operation is implic-

itly defined to be in Block 1. If the IAP operation originates

physically from Block 1, then the target address is implicitly

defined to be in Block 0. If the IAP operation originates from

external program space, then, the target will depend on the

address and the state of bank selection.

4.2.3 IAP Enable Bit

The IAP enable bit, SFCF[6], enables in-application pro-

gramming mode. Until this bit is set, all flash programming

IAP commands will be ignored.

4.2.4 In-Application Programming Mode

Commands

All of the following commands can only be initiated in the

IAP mode. In all situations, writing the control byte to the

SFCM register will initiate all of the operations. All com-

mands will not be enabled if the security locks are enabled

on the selected memory block.

The Program command is for programming new data into

the memory array. The portion of the memory array to be

programmed should be in the erased state, FFH. If the

memory is not erased, it should first be erased with an

appropriate Erase command. Warning: Do not attempt to

write (program or erase) to a block that the code is cur-

rently fetching from. This will cause unpredictable pro-

gram behavior and may corrupt program data.

4.2.4.1 Chip-Erase

The Chip-Erase command erases all bytes in both memory

blocks. This command is only allowed when EA#=0 (exter-

nal memory execution). Additionally this command is not

permitted when the device is in level 4 locking. In all other

instances, this command ignores the Security Lock status

and will erase the security lock bits and re-map bits.

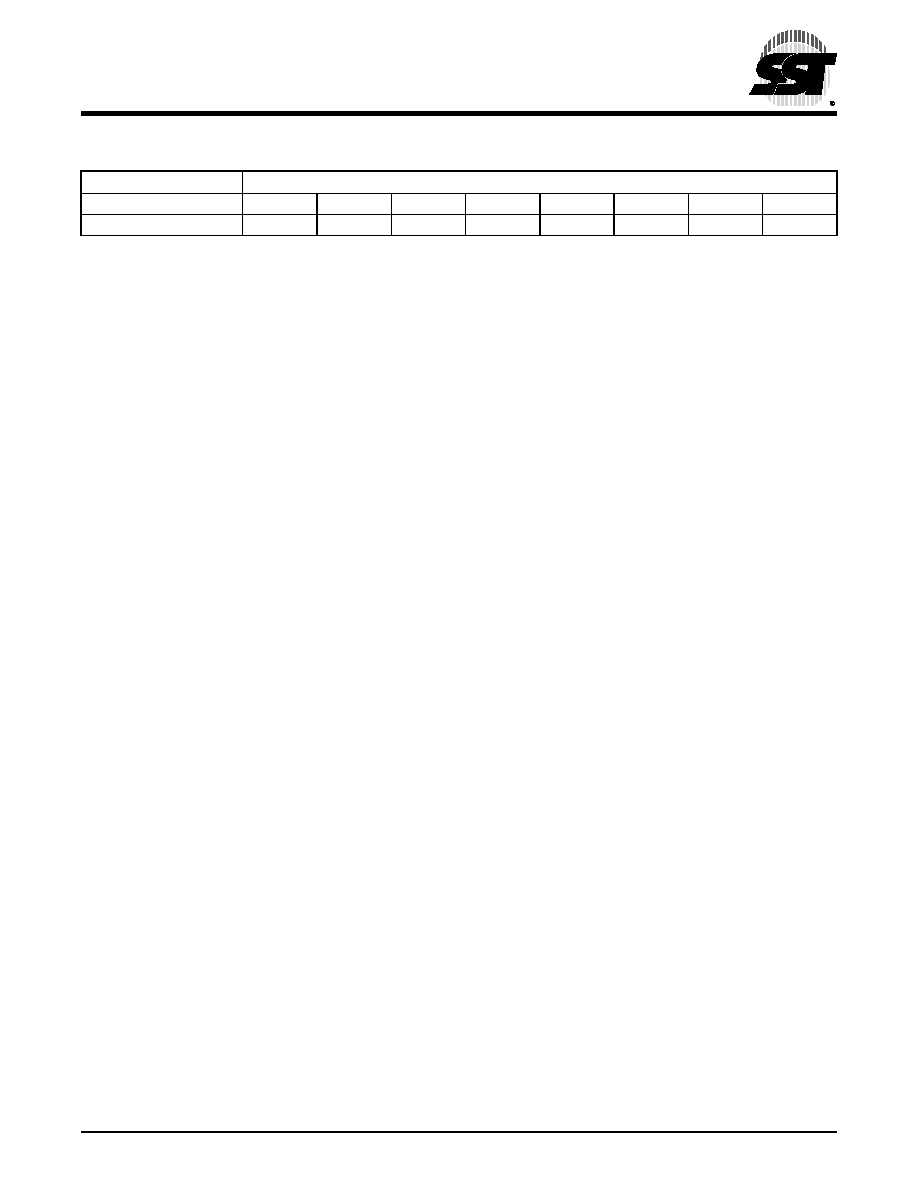

TABLE

4-3: ADDITIONAL READ COMMANDS IN EXTERNAL HOST MODE

Address

Data

60H

X

SC1_i

SC0_i

SB1_i

SB2_i

SB3_i

61H

XXXXXX

EDC_i

X

T4-3.0 1228

相关PDF资料 |

PDF描述 |

|---|---|

| SST89E554A-40-I-TQJ | 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQFP44 |

| SSTE32882HLBAKG | SSTE SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA176 |

| SSTE32882HLBBKG | SSTE SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA176 |

| SSTUA32864EC,557 | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| SSTUA32866EC/G | 32866 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PBGA96 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SST89E554RC | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89E554RC-25-C-NI | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89E554RC-25-C-NJ | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89E554RC-25-C-PI | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

| SST89E554RC-25-C-PJ | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

发布紧急采购,3分钟左右您将得到回复。