- 您现在的位置:买卖IC网 > PDF目录98143 > SSTUB32864EC/G (NXP SEMICONDUCTORS) 32864 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PBGA96 PDF资料下载

参数资料

| 型号: | SSTUB32864EC/G |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 锁存器 |

| 英文描述: | 32864 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PBGA96 |

| 封装: | 13.50 X 5.50 MM, 1.05 MM HEIGHT, LEAD FREE, PLASTIC, SOT-536-1, LFBGA-96 |

| 文件页数: | 19/19页 |

| 文件大小: | 113K |

| 代理商: | SSTUB32864EC/G |

SSTUB32864_2

NXP B.V. 2007. All rights reserved.

Product data sheet

Rev. 02 — 26 March 2007

9 of 19

NXP Semiconductors

SSTUB32864

1.8 V congurable registered buffer for DDR2-800 RDIMM applications

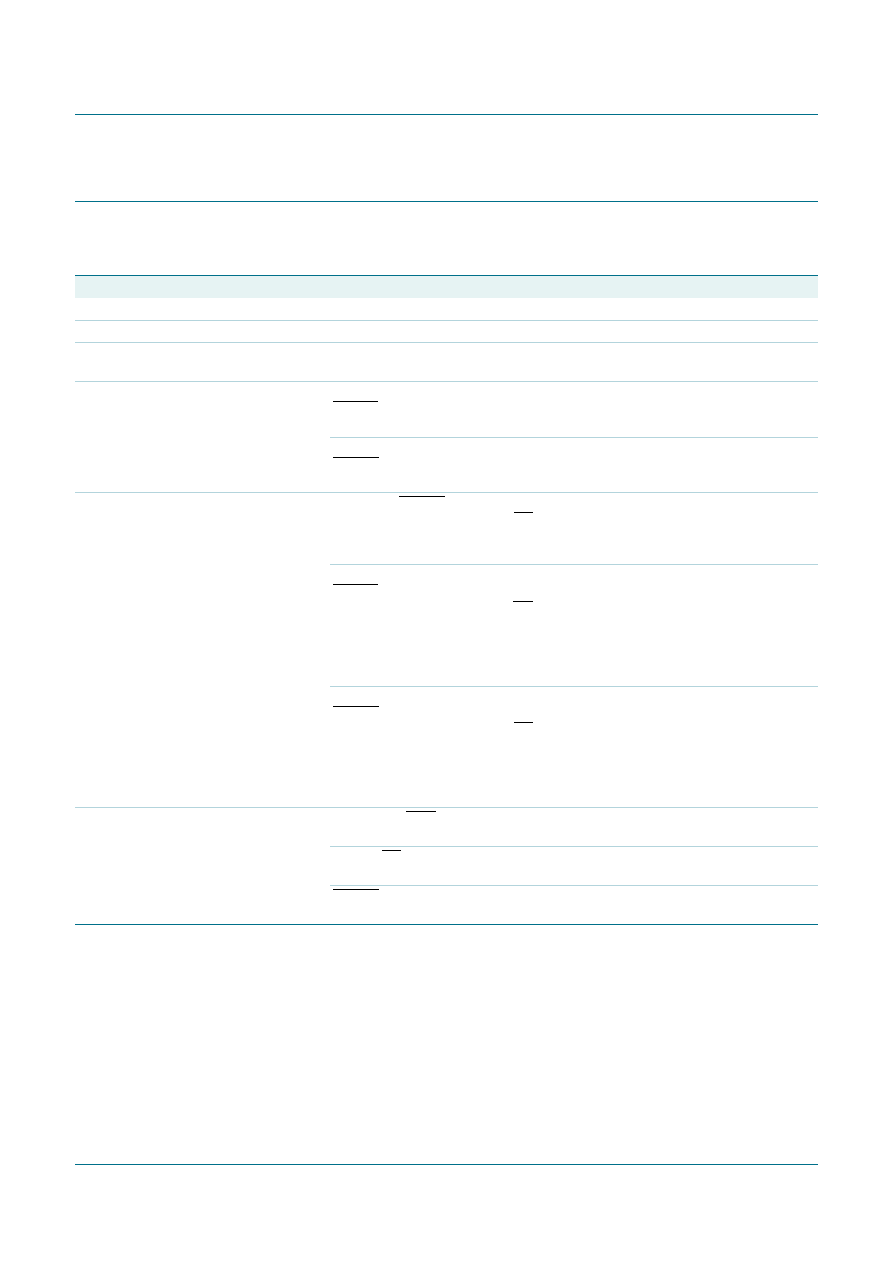

10. Characteristics

Table 6.

Characteristics

Recommended operating conditions; Tamb =0 °Cto+70 °C; all voltages are referenced to GND (ground=0V);

unless otherwise specied.

Symbol

Parameter

Conditions

Min

Typ

Max

Unit

VOH

HIGH-level output voltage

IOH = 6 mA; VDD = 1.7 V

1.2

-

V

VOL

LOW-level output voltage

IOL = 6 mA; VDD = 1.7 V

-

0.5

V

II

input current

all inputs; VI =VDD or GND;

VDD = 2.0 V

5-

+5

A

IDD

supply current

static Standby mode;

RESET = GND; IO = 0 mA;

VDD = 2.0 V

--2

mA

static Operating mode;

RESET = VDD; IO = 0 mA;

VDD = 2.0 V; VI =VIH(AC) or VIL(AC)

--40

mA

IDDD

dynamic operating current

per MHz

clock only; RESET = VDD;

VI =VIH(AC) or VIL(AC); CK and CK

switching at 50 % duty cycle.

IO = 0 mA; VDD = 2.0 V

-16

-

A

per each data input, 1 : 1 mode;

RESET = VDD;

VI =VIH(AC) or VIL(AC); CK and CK

switching at 50 % duty cycle.

One data input switching at half

clock frequency, 50 % duty cycle.

IO = 0 mA; VDD = 2.0 V

-11

-

A

per each data input, 1 : 2 mode;

RESET = VDD;

VI =VIH(AC) or VIL(AC); CK and CK

switching at 50 % duty cycle.

One data input switching at half

clock frequency, 50 % duty cycle.

IO = 0 mA; VDD = 2.0 V

-19

-

A

Ci

input capacitance

data inputs, CSR;

VI =Vref ± 250 mV; VDD = 1.8 V

2.5

-

3.5

pF

CK and CK; VICR = 0.9 V;

VID = 600 mV; VDD = 1.8 V

2-

3pF

RESET; VI =VDD or GND;

VDD = 1.8 V

2-

4pF

相关PDF资料 |

PDF描述 |

|---|---|

| SSTUB32868ET/S | 32868 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA176 |

| SSTUG32865ET/S | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA160 |

| SSTUG32868ET/G | 32868 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PBGA176 |

| SSTUP32866EC/S | 32866 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PBGA96 |

| SSTV16857EC | POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SSTUB32865 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:1.8 V 28-bit 1 : 2 registered buffer with parity for DDR2-800 RDIMM applications |

| SSTUB32865ET/G,518 | 功能描述:寄存器 1.8V 28B REG RoHS:否 制造商:NXP Semiconductors 逻辑类型:CMOS 逻辑系列:HC 电路数量:1 最大时钟频率:36 MHz 传播延迟时间: 高电平输出电流:- 7.8 mA 低电平输出电流:7.8 mA 电源电压-最大:6 V 最大工作温度:+ 125 C 封装 / 箱体:SOT-38 封装:Tube |

| SSTUB32865ET/G-T | 功能描述:寄存器 1.8V 28B REG BUF/PRTY DDR2-800 RoHS:否 制造商:NXP Semiconductors 逻辑类型:CMOS 逻辑系列:HC 电路数量:1 最大时钟频率:36 MHz 传播延迟时间: 高电平输出电流:- 7.8 mA 低电平输出电流:7.8 mA 电源电压-最大:6 V 最大工作温度:+ 125 C 封装 / 箱体:SOT-38 封装:Tube |

| SSTUB32866 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:1.8 V 25-bit 1 : 1 or 14-bit 1 : 2 configurable registered buffer with parity for DDR2-800 RDIMM applications |

| SSTUB32866_10 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:1.8 V 25-bit 1 : 1 or 14-bit 1 : 2 configurable registered buffer with parity for DDR2-800 RDIMM applications |

发布紧急采购,3分钟左右您将得到回复。