- 您现在的位置:买卖IC网 > PDF目录98143 > ST52T430K3B6 (STMICROELECTRONICS) 8-BIT, OTPROM, 20 MHz, MICROCONTROLLER, PDIP32 PDF资料下载

参数资料

| 型号: | ST52T430K3B6 |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, OTPROM, 20 MHz, MICROCONTROLLER, PDIP32 |

| 封装: | PLASTIC, SDIP-32 |

| 文件页数: | 60/85页 |

| 文件大小: | 1192K |

| 代理商: | ST52T430K3B6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页当前第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页

ST52T430/E430

63/85

When the SCI Receiver is in IDLE status, it is

waiting for the START condition, which is obtained

with a logic level 0, consecutive to a logic level 1.

This condition is detected if a logic level 0 is

sampled after three logic levels 1 with the fixed

sampling time.

The recognition of the START bit forces the SCI

Receiver Block to enter in a data acquisition

sequence. The data acquisition sequence is

configured via Configuration Register 20 as

follows.

The 2 bits, M, of the Configuration Register 20

allows the definition of the serial mode as

illustrated in Table 11.1.

In the case that M=10,

Βιτ Τ8 is used to set the

parity check in order to perform (as indicated in

Recognition of the STOP condition allows data

received

from

the

Recovery

Buffer

to

be

transferred to the SCDR_RX buffer, adding the

eventual ninth data bit, according to the meaning

illustrated in previous Table 11.1. After this

operation, the RXF flag of the SCI Status Input

Register 19 (Figure 11.3) is set to logic level 1. The

Control Unit reads data from the SCDR_RX buffer

(in read-only mode) with the LDRI instruction,

addressing Input Register 18, and provides a reset

at logic level 0 to the RXF flag.

If data of the Recovery Buffer is ready to be

transferred into the SCDR_RX buffer, but the

previous one was not read by the Core yet, an

OVERRUN Error takes place: the status flag

OVERR indicates the error condition. In this case,

the information stored in the SCDR_RX buffer is

not altered, but the one that has caused the

OVERRUN error can be overwritten by new data

deriving from the serial data line.

Recovery Buffer Block

This block is structured as a synchronized finite

state machine on the CLOCK_RX signal.

When the Recovery Buffer Block is in IDLE state it

waits for the reception of the correct 1 and 0

sequence representing START.

The recognition takes place by sampling the input

RX/PC5 at CLOCK_RX frequency, which has a

frequency that is 16 times higher than CLOCK_TX.

While the external transmitter sends a single bit,

the Recovery Buffer Block samples 16 states (from

SAMPLE1 to SAMPLE16).

The analysis of the RX/PC5 input signal is carried

out providing three samples for each bit received.

If these three samples are not equal, then the

noise error flag, NSERR, of Input Register 19 is set

to 1 and the data value received will be the one

assumed by the majority of the samples.

The procedure above allows SCI not to become

IDLE, because of a limited noise due to “an

erroneous

sampling”.

The

transmission

is

recognized as correct and the noise flag is set.

At the end of the reception of a bit, Recovery Buffer

Block will repeat the same step 9 times: one for the

stop acquisition (10 times in case of 9-bit data,

double stop or parity check).

At the end of data reception the Recovery Buffer

Block will supply information on eventual frame

errors by setting the FRERR flag bit of Input

Register 19 to 1.

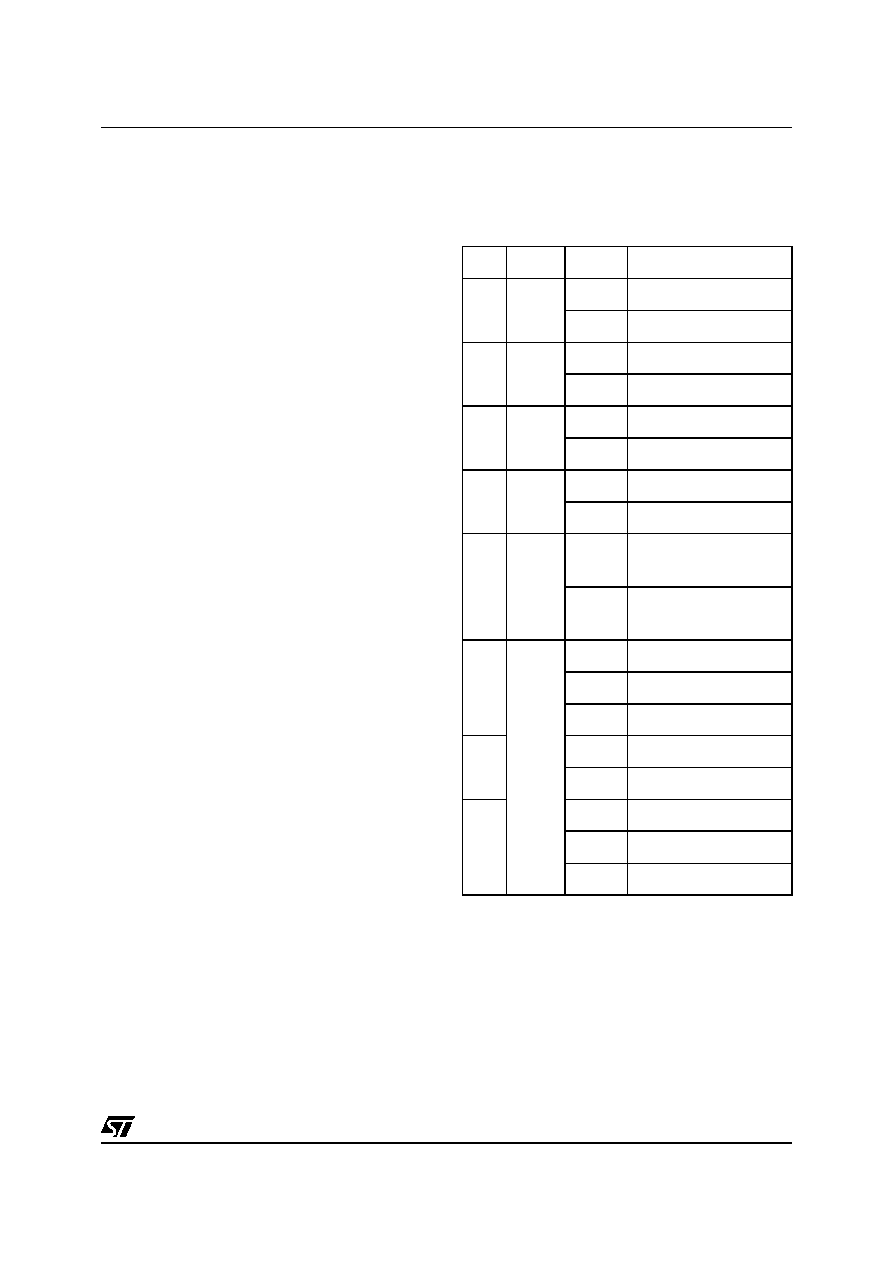

Table 11.1 Configuration Register 20 Setting

Bit

Name

Value

Description

0TE

0

Transmission

1

Transmission ENABLED

1RE

0

Receiver DISABLED

1

Receiver ENABLED

2M

00

8, No Parity, 1 bit stop

01

8, No Parity, 2 bit stop

3

10

8, Parity, 1 bit stop

11

9, No Parity, 1 bit stop

4T8

0

Parity Odd, if Parity is

selected (M

= 10);

otherwise 9th Data bit

1

Parity Even, if Parity is

selected (M = 10);

otherwise 9th Data bit

5

BRSL

000

600 baud

001

1200 baud

010

2400baud

6

011

4800 baud

100

9600 baud

7

101

19200 baud

110

38400 baud

111

Not Used

相关PDF资料 |

PDF描述 |

|---|---|

| ST52T430K3T6 | 8-BIT, OTPROM, 20 MHz, MICROCONTROLLER, PQFP32 |

| ST5X86V12HS | 64-BIT, 120 MHz, MICROPROCESSOR, CPGA168 |

| ST6235Q6 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP52 |

| ST6240BQ6/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP80 |

| ST6242BQ1/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST52T430K3M6 | 制造商:STMicroelectronics 功能描述: |

| ST52T430K3T6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Three Timer/PWMs, ADC, SCI |

| ST52T440 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Timer/PWM, Analog Comparator, Triac/PWM Timer, WDG |

| ST52T440F0B6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Timer/PWM, Analog Comparator, Triac/PWM Timer, WDG |

| ST52T440F0M6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Timer/PWM, Analog Comparator, Triac/PWM Timer, WDG |

发布紧急采购,3分钟左右您将得到回复。