- 您现在的位置:买卖IC网 > PDF目录98143 > ST52T430K3B6 (STMICROELECTRONICS) 8-BIT, OTPROM, 20 MHz, MICROCONTROLLER, PDIP32 PDF资料下载

参数资料

| 型号: | ST52T430K3B6 |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, OTPROM, 20 MHz, MICROCONTROLLER, PDIP32 |

| 封装: | PLASTIC, SDIP-32 |

| 文件页数: | 62/85页 |

| 文件大小: | 1192K |

| 代理商: | ST52T430K3B6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页当前第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页

ST52T430/E430

65/85

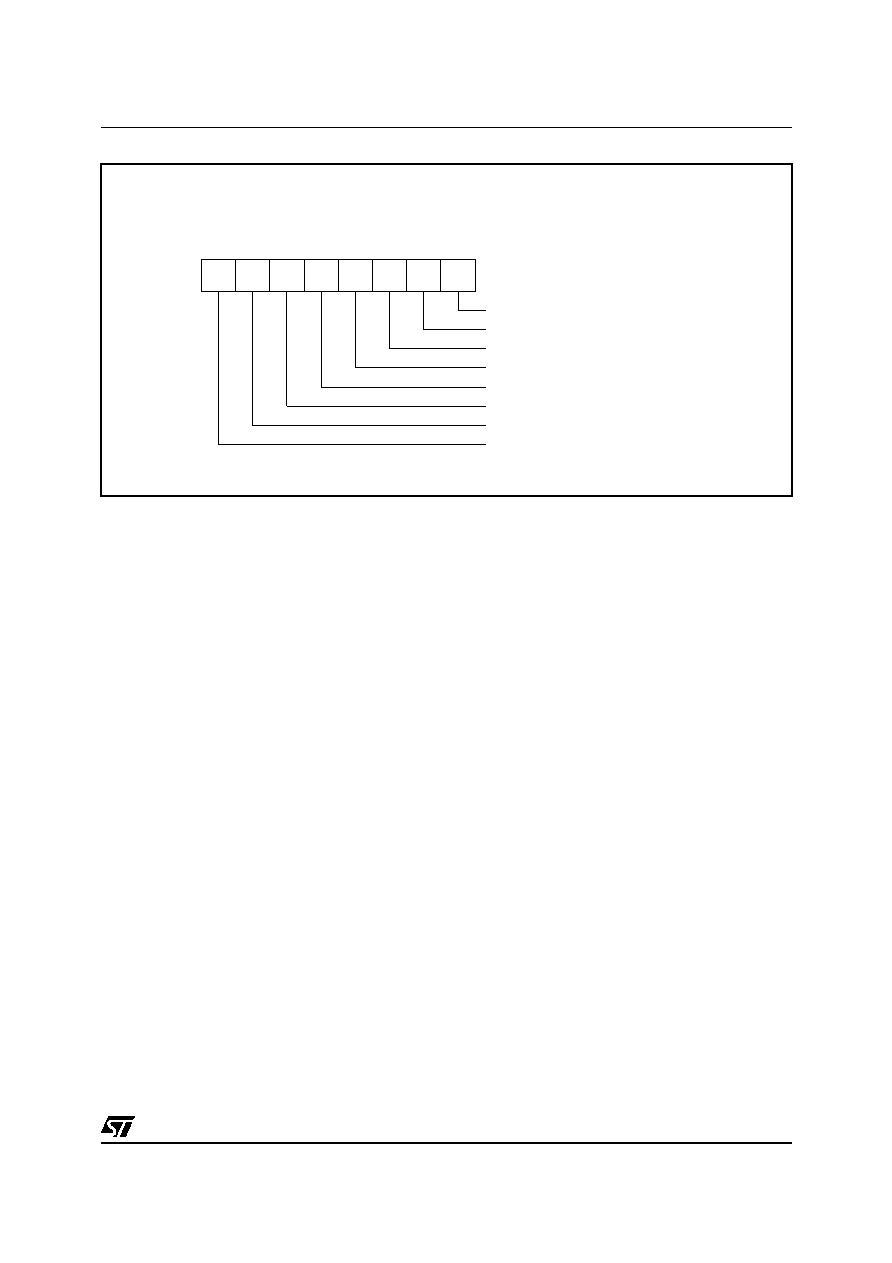

Figure 11.3 SCI Status Input Register

After a RESET signal RST, the SCDR_TX block is

in IDLE state until it receives the enabling signal

TE=1, of Configuration Register 20.

Data is loaded on the peripheral register (OR 9) by

using the instruction LPPR or LDPE. If TE=1 the

data to be transmitted is transferred from DR_TX

block and flag of Input Register 19. TXEM is reset

to 0 in order to indicate that the SCDR_TX block is

full.

If the core supplies new data it can’t be loaded in

the SCDR_TX block until the current data hasn’t

been unloaded on the Shift Register block.

Therefore, data may be loaded in the SCDR_TX

Block only when TXEM is 1.

When the SHIFT REGISTER Block loads data to

be transmitted on an internal buffer, TXEND is

reset to 0 in order to indicate the beginning of a

new transmission. At the end of transmission

TXEND is set to 1, allowing to load new data

coming from SCDR_TX in the SHIFT REGISTER.

Note: TXEND = 1 does not mean SCDR_TX is

ready to receive new data. For this reason it is

better to utilize the TXEM signal in order to

synchronize the LDPR instruction to the SCI

TRANSMITTER block

If the ST52x430 core resets TE to 0, the

transmission is interrupted, but the SCI Transmitter

block completes the transmission in progress

before reset.

Warning: after the stop bit in SCI transmission an

idle time is present before the next start bit. This

time is equal to the duration of a bit transmission.

11.3 Baud Rate Generator Block

The Baud Rate Generator Block performs the

division of the clock master signal (CKM), in a set

of synchronism frequencies for the serial bit

reception/transmission on the external line.

Table 11.1 illustrates the set of frequencies

selected

by

means

of

BRSL

(Configuration

Register 20).

Reception frequency (CLOCK_RX) is 16 times

higher than transmission frequency (CLOCK_TX).

The following example illustrates a simple way to

use SCI to receive and transmit data:

LDRC 1 155

LDCR 20 1

These instructions load value 155

on the Configuration Register 20

fixing the Baud Rate=9600, 8 bit

data, TE=1, RE=1; Parity; 1 stop bit.

LDRC 1 252

LDCR 19 4

SCI

Interrupts

enabled,

clock

frequency 20 MHz

LDRC 1 170

LDPR 9 1

Send data to transmission buffer

WAITI

LDRI 6 19

Save the SCI status register on the

RAM

LDRI 1 18

Save the received data on a RAM

register

D7 D6 D5 D4 D3 D2 D1 D0

SCI_ST

Input Register 19

TXEND

- END TRANSMISSION

TXEM

- TRANSMISSION DATA REGISTER EMPTY

R8

- RECEIVED NINTH BIT

NSERR

- NOISE ERROR

NOT USED

OVERR - OVERRUN ERROR

RXF

- RECEIVE DATA REGISTER FULL

FRERR

- FRAME ERROR

相关PDF资料 |

PDF描述 |

|---|---|

| ST52T430K3T6 | 8-BIT, OTPROM, 20 MHz, MICROCONTROLLER, PQFP32 |

| ST5X86V12HS | 64-BIT, 120 MHz, MICROPROCESSOR, CPGA168 |

| ST6235Q6 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP52 |

| ST6240BQ6/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP80 |

| ST6242BQ1/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST52T430K3M6 | 制造商:STMicroelectronics 功能描述: |

| ST52T430K3T6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Three Timer/PWMs, ADC, SCI |

| ST52T440 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Timer/PWM, Analog Comparator, Triac/PWM Timer, WDG |

| ST52T440F0B6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Timer/PWM, Analog Comparator, Triac/PWM Timer, WDG |

| ST52T440F0M6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Timer/PWM, Analog Comparator, Triac/PWM Timer, WDG |

发布紧急采购,3分钟左右您将得到回复。