- 您现在的位置:买卖IC网 > PDF目录361344 > T431616E-7SG (TM Technology, Inc.) 1M x 16 SDRAM 512K x 16bit x 2Banks Synchronous DRAM PDF资料下载

参数资料

| 型号: | T431616E-7SG |

| 厂商: | TM Technology, Inc. |

| 英文描述: | 1M x 16 SDRAM 512K x 16bit x 2Banks Synchronous DRAM |

| 中文描述: | 100万× 16内存为512k × 16Bit的X 2Banks同步DRAM |

| 文件页数: | 20/74页 |

| 文件大小: | 781K |

| 代理商: | T431616E-7SG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页

TE

CH

tm

LVTTL Interface

T431616D/E

TM Technology Inc. reserves the right

P. 20

to change products or specifications without notice.

Publication Date: FEB. 2007

Revision: A

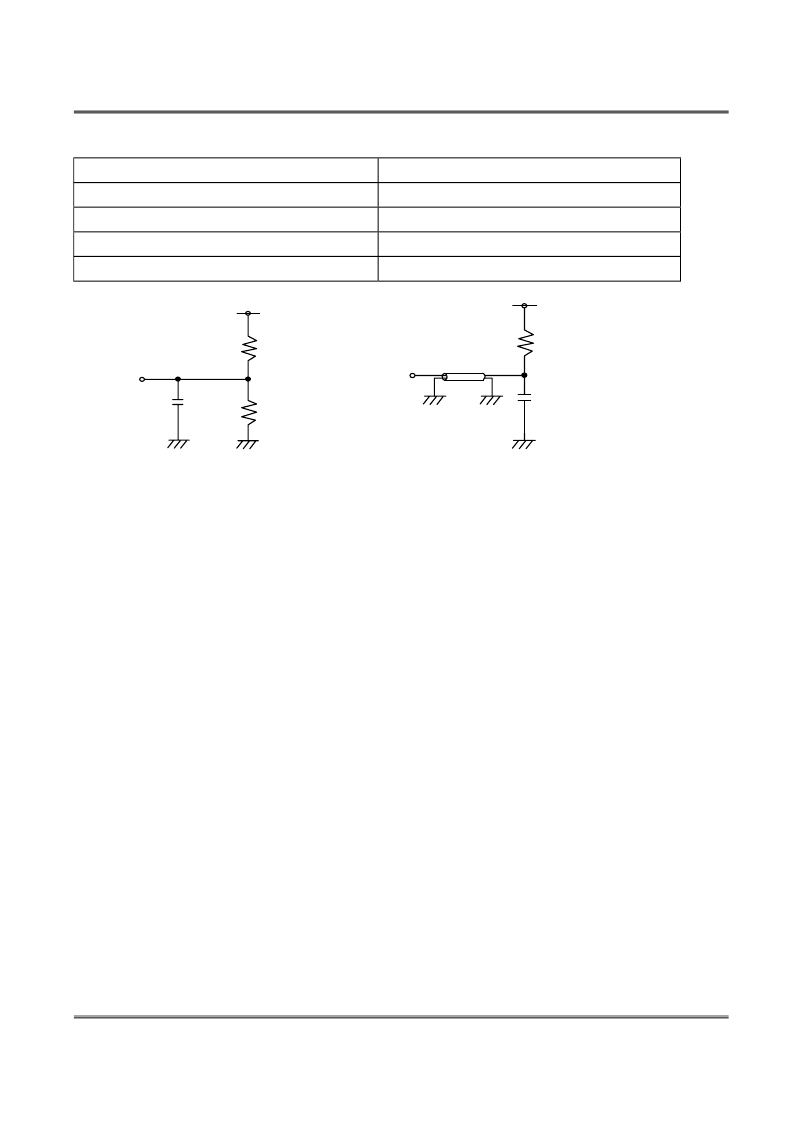

Reference Level of Output Signals

1.4V / 1.4V

Output Load

Reference to the Under Output Load (B)

Input Signal Levels

2.4V / 0.4V

Transition Time (Rise and Fall) of Input Signals

1ns

Reference Level of Input Signals

1.4V

7. Transition times are measured between V

IH

and V

IL

. Transition(rise and fall) of input signals are in a fixed slope (1 ns).

3.3V

1.2k

870

30pF

Output

1.4V

50

Output

30pF

50

Z0=

LVTTL D.C. Test Load (A)

LVTTL A.C. Test Load (B)

8. t

HZ

defines the time in which the outputs achieve the open circuit condition and are not at reference levels.

9. These parameters account for the number of clock cycle and depend on the operating frequency of the clock as follows:

the number of clock cycles = specified value of timing/Clock cycle time

(count fractions as a whole number)

10.If clock rising time is longer than 1 ns, ( t

R

/ 2 -0.5) ns should be added to the parameter.

11.Assumed input rise and fall time t

T

( t

R

& t

F

) = 1 ns

If t

R

or t

F

is longer than 1 ns, transient time compensation should be considered, i.e., [(tr + tf)/2 - 1] ns should be

added to the parameter.

12. Power up Sequence

Power up must be performed in the following sequence.

1) Power must be applied to V

DD

and V

DDQ

(simultaneously) when all input signals are held "NOP" state and both

CKE = "H" and LDQM/UDQM = "H." The CLK signals must be started at the same time.

2) After power-up, a pause of 200us minimum is required. Then, it is recommended that LDQM/UDQM is held

"HIGH" (V

DD

levels) to ensure DQ output is in high impedance.

3) Both banks must be precharged.

4) Mode Register Set command must be asserted to initialize the Mode register.

5) A minimum of 2 Auto-Refresh dummy cycles must be required before or after the Mode Register Set command

in step 4 to stabilize the internal circuitry of the device.

相关PDF资料 |

PDF描述 |

|---|---|

| T436416A | 4M X 16 SDRAM |

| T436416A-10S | 4M X 16 SDRAM |

| T436416A-10SG | Terminal Block End Barrier; For Use With:AB1 Series Terminal Blocks; Accessory Type:End Barrier; Leaded Process Compatible:Yes; Peak Reflow Compatible (260 C):Yes RoHS Compliant: Yes |

| T436416A-6S | 4M X 16 SDRAM |

| T436416A-6SG | 4M X 16 SDRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| T4322 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:TRIANGULAR TYPE |

| T4323 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:TRIANGULAR TYPE |

| T4333 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:TRIANGULAR TYPE |

| T43331G | 制造商:BITECH 制造商全称:Bi technologies 功能描述:Thick Film Super Low Profile SIP Resistor Networks |

| T43331J | 制造商:BITECH 制造商全称:Bi technologies 功能描述:Thick Film Super Low Profile SIP Resistor Networks |

发布紧急采购,3分钟左右您将得到回复。