- 您现在的位置:买卖IC网 > PDF目录1970 > TMS320VC5409GGU100 (Texas Instruments)IC DIG SIG PROCESSOR 144-BGA PDF资料下载

参数资料

| 型号: | TMS320VC5409GGU100 |

| 厂商: | Texas Instruments |

| 文件页数: | 74/93页 |

| 文件大小: | 0K |

| 描述: | IC DIG SIG PROCESSOR 144-BGA |

| 标准包装: | 160 |

| 系列: | TMS320C54x |

| 类型: | 定点 |

| 接口: | 主机接口,McBSP |

| 时钟速率: | 100MHz |

| 非易失内存: | ROM(32 kB) |

| 芯片上RAM: | 64kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.80V |

| 工作温度: | -40°C ~ 100°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-LFBGA |

| 供应商设备封装: | 144-BGA MICROSTAR(12x12) |

| 包装: | 托盘 |

| 配用: | 296-15829-ND - DSP STARTER KIT FOR TMS320C5416 |

| 其它名称: | 296-10763 296-10763-5 296-10763-5-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页当前第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页

Documentation Support

76

April 1999 Revised October 2008

SPRS082F

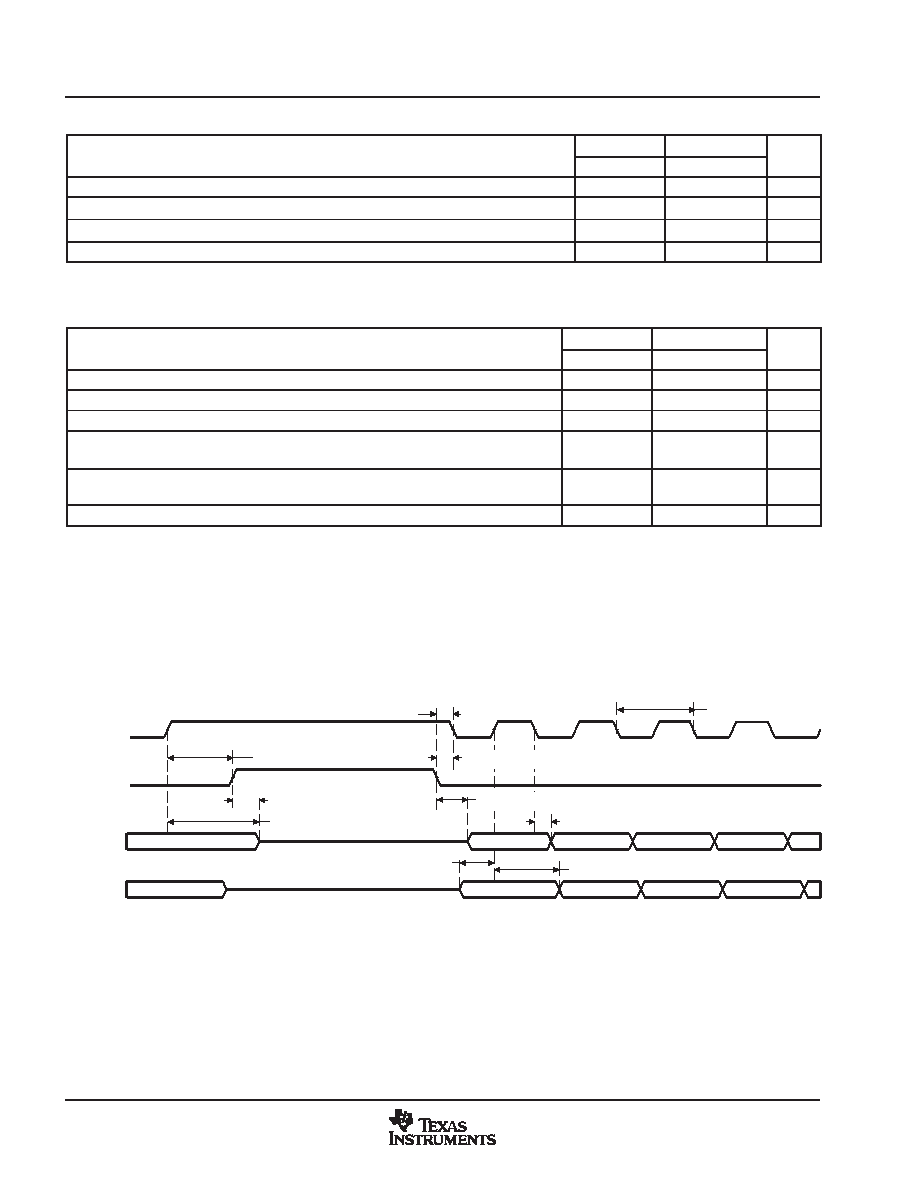

Table 527. McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 10b, CLKXP = 1)

MASTER

SLAVE

UNIT

MIN

MAX

MIN

MAX

UNIT

tsu(BDRV-BCKXH)

Setup time, BDR valid before BCLKX high

10

12H

ns

th(BCKXH-BDRV)

Hold time, BDR valid after BCLKX high

0

5 + 12H

ns

tsu(BFXL-BCKXL)

Setup time, BFSX low before BCLKX low

10

ns

tc(BCKX)

Cycle time, BCLKX

32H

ns

For all SPI slave modes, CLKG is programmed as 1/2 of the CPU clock by setting CLKSM = CLKGDV = 1.

Table 528. McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 10b, CLKXP = 1)

PARAMETER

MASTER

SLAVE

UNIT

PARAMETER

MIN

MAX

MIN

MAX

UNIT

th(BCKXH-BFXL)

Hold time, BFSX low after BCLKX high§

T 4

T + 4

ns

td(BFXL-BCKXL)

Delay time, BFSX low to BCLKX low

D 5

D + 3

ns

td(BCKXL-BDXV)

Delay time, BCLKX low to BDX valid

3

7

6H + 5

10H + 14

ns

tdis(BCKXH-BDXHZ)

Disable time, BDX high impedance following last data bit from

BCLKX high

D 2

D + 3

ns

tdis(BFXH-BDXHZ)

Disable time, BDX high impedance following last data bit from

BFSX high

2H + 3

6H + 17

ns

td(BFXL-BDXV)

Delay time, BFSX low to BDX valid

4H 2

8H + 17

ns

For all SPI slave modes, CLKG is programmed as 1/2 of the CPU clock by setting CLKSM = CLKGDV = 1.

T = BCLKX period = (1 + CLKGDV) * 2H

D =

BCLKX high pulse width = T/2 when CLKGDV is odd or zero and = (CLKGDV/2 + 1) * 2H when CLKGDV is even

§ FSRP = FSXP = 1. As a SPI master, BFSX is inverted to provide active-low slave-enable output. As a slave, the active-low signal input on BFSX

and BFSR is inverted before being used internally.

CLKXM = FSXM = 1, CLKRM = FSRM = 0 for master McBSP

CLKXM = CLKRM = FSXM = FSRM = 0 for slave McBSP

BFSX should be low before the rising edge of clock to enable slave devices and then begin a SPI transfer at the rising edge of the master clock

(BCLKX).

tsu(BFXL-BCKXL)

th(BCKXH-BDRV)

tdis(BFXH-BDXHZ)

tdis(BCKXH-BDXHZ)

Bit 0

Bit(n-1)

(n-2)

(n-3)

(n-4)

Bit 0

Bit(n-1)

(n-2)

(n-3)

(n-4)

BCLKX

BFSX

BDX

BDR

td(BFXL-BCKXL)

td(BFXL-BDXV)

td(BCKXL-BDXV)

tsu(BDRV-BCKXH)

th(BCKXH-BFXL)

LSB

MSB

tc(BCKX)

Figure 525. McBSP Timing as SPI Master or Slave: CLKSTP = 10b, CLKXP = 1

相关PDF资料 |

PDF描述 |

|---|---|

| TMS470R1A384PZQ | IC RISC MCU 384K FLASH 100-LQFP |

| TMX320DM365BZCE | IC DIGITAL MEDIA SOC 338NFBGA |

| TMX320F28069UPFPA | IC MCU 32BIT 128KB FLASH 80HTQFP |

| TPS2371PWRG4 | IC PWR INTRFCE SW FOR POE 8TSSOP |

| TS3A24157RSERG4 | IC SWITCH DUAL SPDT 10UQFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TMS320VC5409GGU-80 | 功能描述:数字信号处理器和控制器 - DSP, DSC Fixed-Pt Dig Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| TMS320VC5409PGE100 | 功能描述:数字信号处理器和控制器 - DSP, DSC Fixed-Pt Dig Sig Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| TMS320VC5409PGE100 | 制造商:Texas Instruments 功能描述:Digital Signal Processor IC |

| TMS320VC5409PGE-80 | 功能描述:数字信号处理器和控制器 - DSP, DSC Fixed-Pt Dig Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| TMS320VC5409ZGU100 | 功能描述:数字信号处理器和控制器 - DSP, DSC Fixed-Pt Dig Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。