- 您现在的位置:买卖IC网 > PDF目录18733 > TRC101 (RFM)RFIC TRANCEIVER MULTI-CHANNEL FS PDF资料下载

参数资料

| 型号: | TRC101 |

| 厂商: | RFM |

| 文件页数: | 27/42页 |

| 文件大小: | 0K |

| 描述: | RFIC TRANCEIVER MULTI-CHANNEL FS |

| 产品变化通告: | RFIC Obsolescence 15/Sept/2009 |

| 标准包装: | 1 |

| 系列: | TRC |

| 频率: | 300MHz ~ 1GHz |

| 数据传输率 - 最大: | 256kbps |

| 调制或协议: | FSK |

| 应用: | 通用 |

| 功率 - 输出: | 8dBm |

| 灵敏度: | -105dBm |

| 电源电压: | 2.2 V ~ 5.4 V |

| 电流 - 接收: | 17mA |

| 电流 - 传输: | 28mA |

| 数据接口: | PCB,表面贴装 |

| 天线连接器: | PCB,表面贴装 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 16-TSSOP(0.173",4.40mm 宽) |

| 包装: | 标准包装 |

| 其它名称: | 583-1093-6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页

�� �

�

�

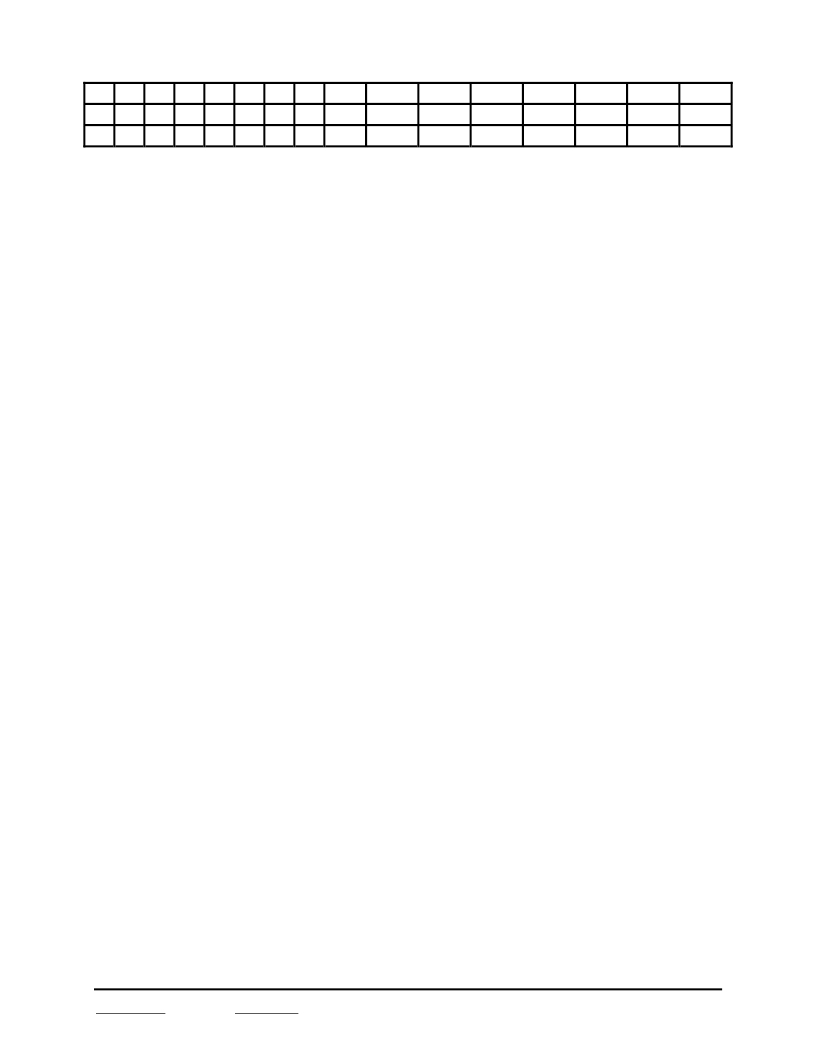

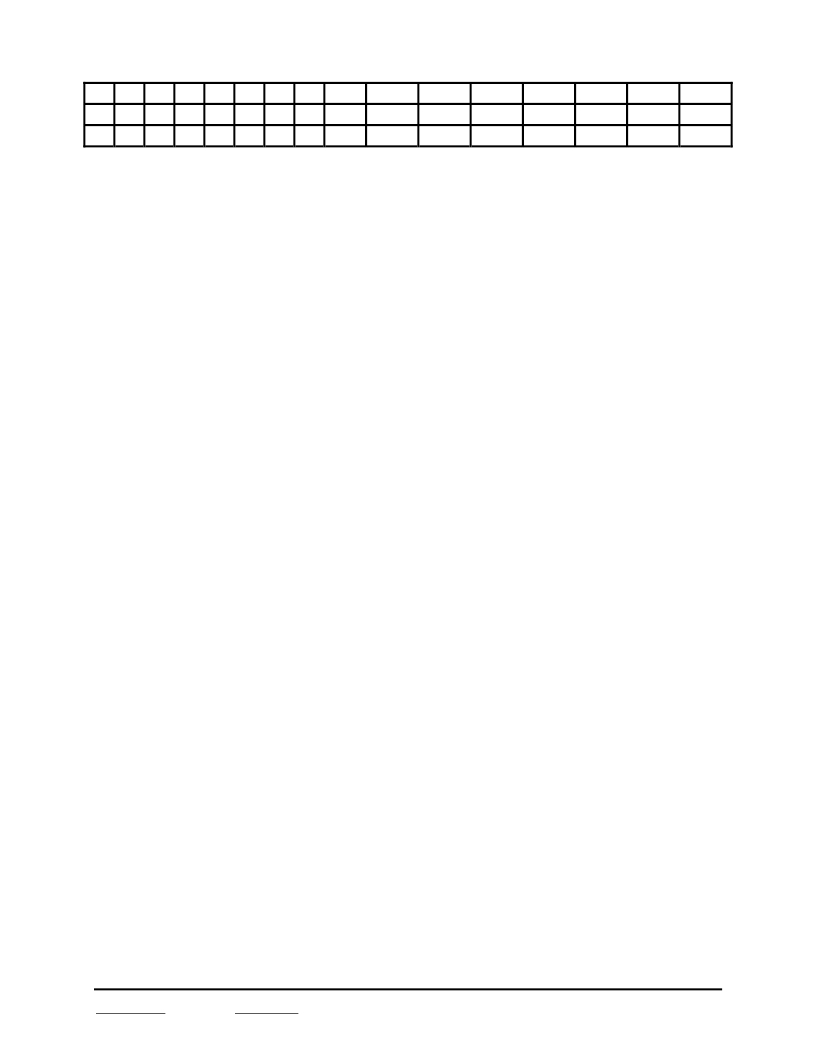

�Data� Rate� Setup� Register� [POR=C623h]�

�Bit�

�15�

�1�

�Bit�

�14�

�1�

�Bit�

�13�

�0�

�Bit�

�12�

�0�

�Bit�

�11�

�0�

�Bit�

�10�

�1�

�Bit�

�9�

�1�

�Bit�

�8�

�0�

�Bit�

�7�

�PRE�

�Bit�

�6�

�BITR6�

�Bit�

�5�

�BITR5�

�Bit�

�4�

�BITR4�

�Bit�

�3�

�BITR3�

�Bit�

�2�

�BITR2�

�Bit�

�1�

�BITR1�

�Bit�

�0�

�BITR0�

�The� Data� Rate� Setup� Register� configures:�

�?�

�?�

�?�

�Expected� data� rate� for� the� receiver�

�Prescaler�

�Effects� of� the� data� rate� on� clock� recovery�

�Bit� [15..8]� -� Command� Code� :� These� bits� are� the� command� code� that� is� sent� serially� to� the� processor� that�

�identifies� the� bits� to� be� written� to� the� Data� Rate� Setup� Register.�

�Bit� [7]� –� Prescaler� Enable� :� When� set� this� bit� enables� the� prescaler� to� obtain� smaller� values� of� expected�

�data� rates.� The� prescaler� value� is� approximately� 1/8.�

�Bit� [6..0]� –� Data� Rate� Parameter� Value� :� These� bits� represent� the� decimal� value� of� the� 7-bit� parameter�

�used� to� calculate� the� expected� data� rate.� To� calculate� the� expected� data� rate,� use� the� following� formula:�

�DR� exp� (kbps)� =� 10000� /� [29� *� (BITR[6..0]+1)� *� (1+PRE*7)]�

�where� BITR[6..0]� is� the� decimal� value� 0� to� 127� and� the� prescaler� (PRE)� is� ‘1’� (on)� or� ‘0’� (off).�

�To� calculate� the� BITR[6..0]� decimal� value� for� a� given� bit� rate,� use� the� following� formula:�

�BITR[6..0]� =� 10000� /� [29� *� (1+PRE*7)� *� DR� exp� ]� -1�

�where� DRexp� is� the� expected� data� rate� and� PRE� is� defined� above.�

�Without� the� prescaler,� the� definable� data� rates� range� from� 2.694kpbs� to� 344.828kbps.� With� the� prescaler�

�enabled,� the� definable� data� rates� range� from� 337� bps� to� 43.103kpbs.�

�The� Slow� clock� recovery� mode� requires� more� accurate� bit� timing� when� setting� the� data� rate.� To� calculate�

�the� accuracy� of� the� data� rate� for� both� Fast� and� Slow� mode,� use� the� following:�

�Slow� mode� Acc� =� Δ� BR/BR� <� 1/(29� *� N)�

�Fast� mode� =� Δ� BR/BR� <� 3/(29� *� N)�

�where� N� is� the� longest� number� of� expected� ones� or� zeros� in� the� data� stream,� Δ� BR� is� the� difference� in� the�

�actual� data� rate� vs.� the� set� data� rate� in� the� transmitter,� and� BR� is� the� expected� data� rate� as� set� above�

�using� BITR[6..0].�

�www.RFM.com�

�Email:� info@rfm.com�

�Page� 27� of� 42�

�?by� RF� Monolithics,� Inc.�

�TRC101� -� 4/8/08�

�相关PDF资料 |

PDF描述 |

|---|---|

| MAX2051ETP+ | IC UP/DOWNCONVERSION MIXR 20TQFN |

| MAX9986ETP+ | IC MIXER DOWN CONV 20-TQFN |

| MAX9994ETP+ | IC MIXER DOWN CONV 20-TQFN |

| MAX9986AETP+ | IC MIXER DOWN CONV 20-TQFN |

| GLDC07B | SWTCH TOP PLNGR SNAP SPDT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TRC10-103 | 制造商:RCD 制造商全称:RCD COMPONENTS INC. 功能描述:RADIAL LEAD TANGOLDTM CAPACITORS EPOXY RESIN COATED, TANTALUM |

| TRC10-104 | 制造商:RCD 制造商全称:RCD COMPONENTS INC. 功能描述:RADIAL LEAD TANGOLDTM CAPACITORS EPOXY RESIN COATED, TANTALUM |

| TRC10-105 | 制造商:RCD 制造商全称:RCD COMPONENTS INC. 功能描述:RADIAL LEAD TANGOLDTM CAPACITORS EPOXY RESIN COATED, TANTALUM |

| TRC10-106 | 制造商:RCD 制造商全称:RCD COMPONENTS INC. 功能描述:RADIAL LEAD TANGOLDTM CAPACITORS EPOXY RESIN COATED, TANTALUM |

| TRC10-107 | 制造商:RCD 制造商全称:RCD COMPONENTS INC. 功能描述:RADIAL LEAD TANGOLDTM CAPACITORS EPOXY RESIN COATED, TANTALUM |

发布紧急采购,3分钟左右您将得到回复。