- 您现在的位置:买卖IC网 > PDF目录275205 > V58C2128164SBLI6 (PROMOS TECHNOLOGIES INC) 8M X 16 DDR DRAM, 0.7 ns, PDSO66 PDF资料下载

参数资料

| 型号: | V58C2128164SBLI6 |

| 厂商: | PROMOS TECHNOLOGIES INC |

| 元件分类: | DRAM |

| 英文描述: | 8M X 16 DDR DRAM, 0.7 ns, PDSO66 |

| 封装: | 0.400 X 0.875 INCH, GREEN, PLASTIC, MS-024FC, TSOP2-66 |

| 文件页数: | 7/60页 |

| 文件大小: | 916K |

| 代理商: | V58C2128164SBLI6 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

15

ProMOS TECHNOLOGIES

V58C2128(804/404/164)SB

V58C2128(804/404/164)SB Rev. 2.2 March 2007

Precharge Operation

The Precharge command is used to deactivate the open row in a particular bank or the open row in all

banks. The bank (s) will be available for a subsequent row access a specified time (tRP) after the precharge

command is issued. Except in the case of concurrent auto precharge, where a READ or WRITE command

to a different bank is allowed as long as it does not interrupt the data transfer in the current bank and does

not violate any other timing parameters. Input A10 determines whether one or all banks are to be precharged,

and in the case where only one bank is to be precharged, inputs BA0, BA1 select the bank. Otherwise BA0,

BA1 are treated as “Don’t Care.” Once a bank has been precharged, it is in the idle state and must be acti-

vated prior to any READ or WRITE commands being issued to that bank. A Precharge command will be treat-

ed as NOP if there is no open row in that bank (idle state), or if the previously open row is already in the

process of precharging.

Auto Precharge Operation

The Auto Precharge operation can be issued by having column address A

10 high when a Read or Write

command is issued. If A

10 is low when a Read or Write command is issued, then normal Read or Write burst

operation is executed and the bank remains active at the completion of the burst sequence. When the Auto

Precharge command is activated, the active bank automatically begins to precharge at the earliest possible

moment during the Read or Write cycle once t

RAS(min) is satisfied. This device supports concurrent auto pre-

charge if the command to the other bank does not interrupt the data transfer to the current bank.

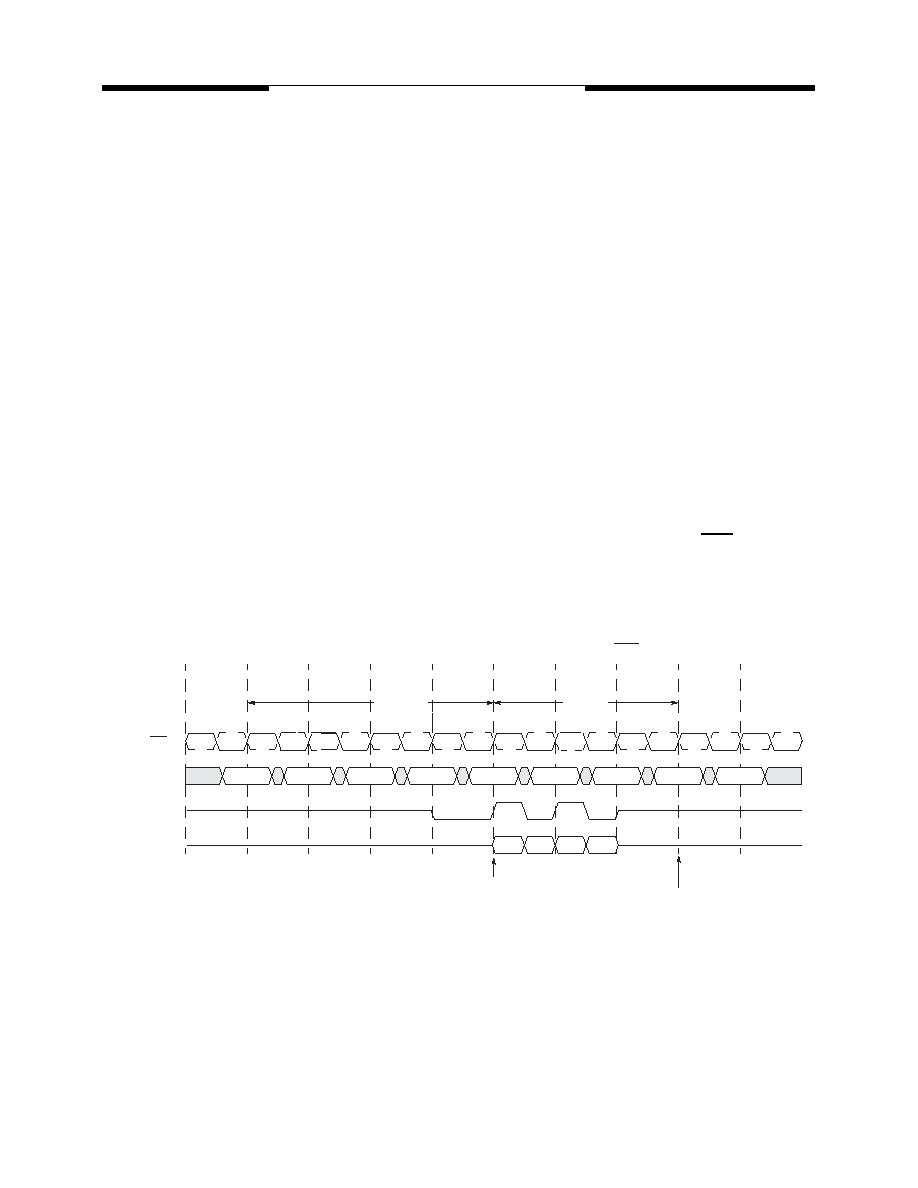

Read with Auto Precharge

If a Read with Auto Precharge command is initiated, the DDR SDRAM will enter the precharge operation

N-clock cycles measured from the last data of the burst read cycle where N is equal to the CAS latency pro-

grammed into the device. Once the autoprecharge operation has begun, the bank cannot be reactivated until

the minimum precharge time (t

RP) has been satisfied.

Read with Autoprecharge Timing

(CAS Latency = 2; Burst Length = 4)

T0

T1

T2

T3

T4

T5

T6

T7

T8

D0

D1

D2

D3

Begin Autoprecharge

BA

ACT

R/w AP

NOP

CK, CK

Command

DQS

DQ

tRAS(min)

tRP(min)

Earliest Bank A reactivate

T9

相关PDF资料 |

PDF描述 |

|---|---|

| V827432U24SATG-B1 | 32M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| V827432U24SATG-D3 | 32M X 72 DDR DRAM MODULE, 0.55 ns, DMA184 |

| V59C1G01164QAUP5H | 64M X 16 DDR DRAM, PBGA92 |

| V59C1G01164QAUF37H | 64M X 16 DDR DRAM, PBGA92 |

| V59C1G01164QALJ19AE | 64M X 16 DDR DRAM, BGA92 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| V58C2128404S | 制造商:MOSEL 制造商全称:MOSEL 功能描述:HIGH PERFORMANCE 2.5 VOLT 128 Mbit DDR SDRAM |

| V58C2128804S | 制造商:MOSEL 制造商全称:MOSEL 功能描述:HIGH PERFORMANCE 2.5 VOLT 128 Mbit DDR SDRAM |

| V58C2256 | 制造商:MOSEL 制造商全称:MOSEL 功能描述:HIGH PERFORMANCE 2.5 VOLT 256 Mbit DDR SDRAM |

| V58C2256164S | 制造商:MOSEL 制造商全称:MOSEL 功能描述:HIGH PERFORMANCE 2.5 VOLT 256 Mbit DDR SDRAM |

| V58C2256324SAB30 | 制造商:Marvell 功能描述:Marvell V58C2256324SAB30 |

发布紧急采购,3分钟左右您将得到回复。