- 您现在的位置:买卖IC网 > PDF目录202172 > V58C2256404SBJ5 (PROMOS TECHNOLOGIES INC) 64M X 4 DDR DRAM, 0.65 ns, PBGA60 PDF资料下载

参数资料

| 型号: | V58C2256404SBJ5 |

| 厂商: | PROMOS TECHNOLOGIES INC |

| 元件分类: | DRAM |

| 英文描述: | 64M X 4 DDR DRAM, 0.65 ns, PBGA60 |

| 封装: | LEAD FREE, MO-233, FBGA-60 |

| 文件页数: | 29/62页 |

| 文件大小: | 983K |

| 代理商: | V58C2256404SBJ5 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页

35

ProMOS TECHNOLOGIES

V58C2256(804/404/164)SB

V58C2256(804/404/164)SB Rev. 1.0 November 2003

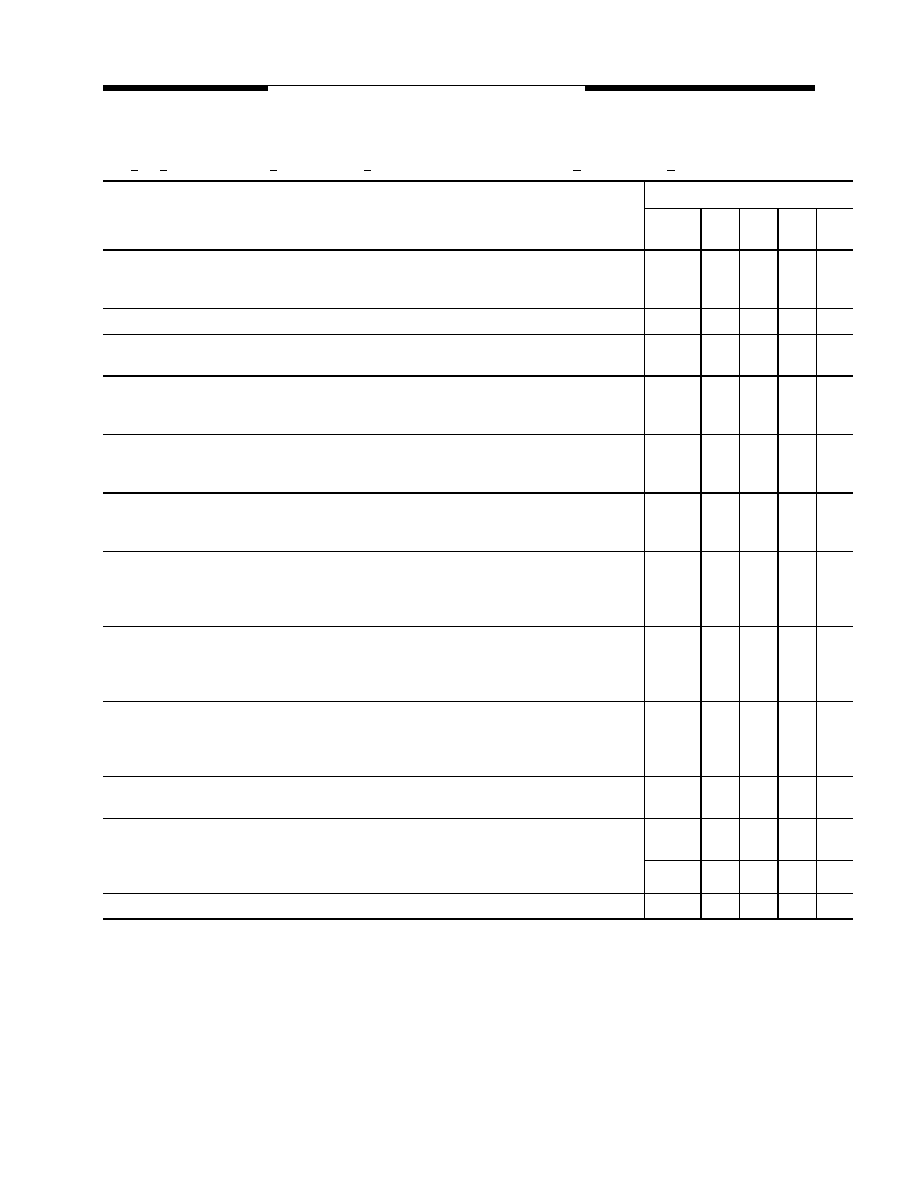

IDD Max Specifications and Conditions

(0°C < TA < 70°C, VDDQ=2.5V+ 0.2V, VDD=2.5 +0.2V, for DDR400 device VDDQ=2.6V+ 0.1V, VDD=2.6 +0.1V)

Conditions

Version

Symbol

-5B/

-5

-6

-7

Unit

Operating current - One bank Active-Precharge; tRC=tRCmin;tCK=100Mhz for DDR200, 133Mhz

for DDR266A & DDR266B, 166Mhz for DDR333B; DQ,DM and DQS inputs changing twice per clock

cycle; address and control inputs changing once per clock cycle

IDD0

120

110

100

mA

Operating current - One bank operation; One bank open, BL=4

IDD1

160

140

120

mA

Precharge power-down standby current; All banks idle; power - down mode; CKE = <VIL(max);

tCK=100Mhz for DDR200, 133Mhz for DDR266A & DDR266B; Vin = Vref for DQ,DQS and DM

IDD2P

302520

mA

Precharge Floating standby current; CS# > =VIH(min);All banks idle; CKE > = VIH(min);

tCK=100Mhz for DDR200, 133Mhz for DDR266A & DDR266B; Address and other control inputs

changing once per clock cycle; Vin = Vref for DQ,DQS and DM

IDD2F

524538

mA

Precharge Quiet standby current; CS# > = VIH(min); All banks idle; CKE > = VIH(min); tCK =

100Mhz for DDR200, 133Mhz for DDR266A & DDR266B; Address and other control inputs stable with

keeping >= VIH(min) or =<VIL(max); Vin = Vref for DQ ,DQS and DM

IDD2Q

504437

mA

Active power - down standby current; one bank active; power-down mode; CKE=< VIL (max); tCK

= 100Mhz for DDR200, 133Mhz for DDR266A & DDR266B, 166MHZ for DDR333B; Vin = Vref for

DQ,DQS and DM

IDD3P

302520

mA

Active standby current; CS# >= VIH(min); CKE>=VIH(min); one bank active; active - precharge;

tRC=tRASmax; tCK = 100Mhz for DDR200, 133Mhz for DDR266A & DDR266B, 166Mhz for

DDR333B; DQ, DQS and DM inputs changing twice per clock cycle; address and other control inputs

changing once per clock cycle

IDD3N

908070

mA

Operating current - burst read; Burst length = 2; reads; continuous burst; One bank active; address

and control inputs changing once per clock cycle; CL=2 at tCK = 100Mhz for DDR200, CL=2 at tCK =

133Mhz for DDR266A, CL=2.5 at tCK = 133Mhz for DDR266B, CL=2.5 at tCK=166Mhz for DDR333B;

50% of data changing at every burst; lout = 0 m A

IDD4R

270

230

190

mA

Operating current - burst write; Burst length = 2; writes; continuous burst; One bank active address

and control inputs changing once per clock cycle; CL=2 at tCK = 100Mhz for DDR200, CL=2 at tCK =

133Mhz for DDR266A, CL=2.5 at tCK = 133Mhz for DDR266B ; DQ, DM and DQS inputs changing

twice per clock cycle, 50% of input data changing at every burst

IDD4W

250

210

170

mA

Auto refresh current; tRC = tRFC(min) - 8*tCK for DDR200 at 100Mhz, 10*tCK for DDR266A

& DDR266B at 133Mhz, 12*tCK for DDR333B; distributed refresh

IDD5

210

200

190

mA

Self refresh current; CKE =< 0.2V; External clock should be on; tCK = 100Mhz for DDR200, 133Mhz

for DDR266A & DDR266B, 166Mhz for DDR333B.

Self refresh current; (Low Power)

IDD6

(normal)

222

mA

(L)

1.2

mA

Operating current - Four bank operation; Four bank interleaving with BL=4

IDD7

400

350

300

mA

相关PDF资料 |

PDF描述 |

|---|---|

| V58C2256164SBLJ5B | 16M X 16 DDR DRAM, 0.65 ns, PBGA60 |

| V58C2256404SCLS7I | 64M X 4 DDR DRAM, 0.75 ns, PBGA60 |

| V58C2256404SHUT6E | 64M X 4 DDR DRAM, PDSO66 |

| V58C2256804SHLJ5E | 32M X 8 DDR DRAM, PBGA60 |

| V58C2256804SHUE6E | 32M X 8 DDR DRAM, PDSO66 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| V58C2256804S | 制造商:MOSEL 制造商全称:MOSEL 功能描述:HIGH PERFORMANCE 2.5 VOLT 256 Mbit DDR SDRAM |

| V58C2256804SAT-5 | 制造商:Mosel Vitelic Corporation 功能描述:SDRAM, DDR, 32M x 8, 66 Pin, Plastic, TSSOP |

| V58C265164S | 制造商:MOSEL 制造商全称:MOSEL 功能描述:64 Mbit DDR SDRAM 2.5 VOLT 4M X 16 |

| V58C265404S | 制造商:MOSEL 制造商全称:MOSEL 功能描述:HIGH PERFORMANCE 2.5 VOLT 16M X 4 DDR SDRAM 4 BANKS X 4Mbit X 4 |

| V58C265804S | 制造商:MOSEL 制造商全称:MOSEL 功能描述:HIGH PERFORMANCE 2.5 VOLT 8M X 8 DDR SDRAM 4 BANKS X 2Mbit X 8 |

发布紧急采购,3分钟左右您将得到回复。