- 您现在的位置:买卖IC网 > PDF目录202172 > V58C2256404SBJ5 (PROMOS TECHNOLOGIES INC) 64M X 4 DDR DRAM, 0.65 ns, PBGA60 PDF资料下载

参数资料

| 型号: | V58C2256404SBJ5 |

| 厂商: | PROMOS TECHNOLOGIES INC |

| 元件分类: | DRAM |

| 英文描述: | 64M X 4 DDR DRAM, 0.65 ns, PBGA60 |

| 封装: | LEAD FREE, MO-233, FBGA-60 |

| 文件页数: | 30/62页 |

| 文件大小: | 983K |

| 代理商: | V58C2256404SBJ5 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页

36

V58C2256(804/404/164)SB Rev. 1.0 November 2003

ProMOS TECHNOLOGIES

V58C2256(804/404/164)SB

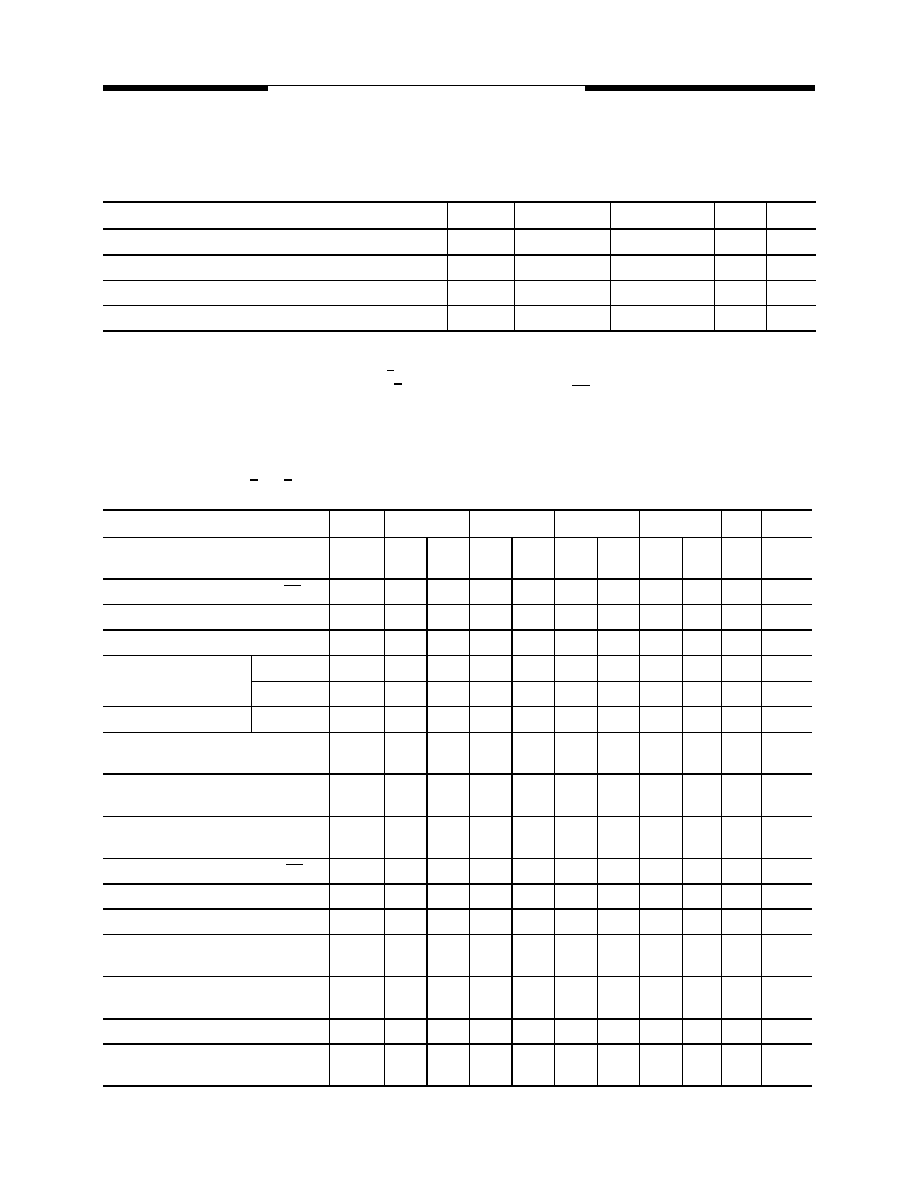

AC Operating Conditions & Timing Specification

AC Operating Conditions

Note:

1.Vih(max) = 4.2V. The overshoot voltage duration is < 3ns at VDD.

2. Vil(min) = -1.5V. The undershoot voltage duration is < 3ns at VSS.

3. VID is the magnitude of the difference between the input level on CK and the input on CK.

4. The value of VIX is expected to equal 0.5*VDDQ of the transmitting device and must track variations in the DC level of the same.

ELECTRICAL CHARACTERISTICS AND AC TIMING for PC400/PC333/PC266 -Absolute Spec-

ifications

(Notes: 1-5, 14-17) (0°C < T A < 70°C; VDDQ = +2.5V ±0.2V, VDD=+2.5V ±0.2V for DDR400 device VDDQ = +2.6V ±0.1V,

VDD=+2.6V ±0.1V)

Parameter/Condition

Symbol

Min

Max

Unit

Note

Input High (Logic 1) Voltage, DQ, DQS and DM signals

VIH(AC)

VREF + 0.31

V

1

Input Low (Logic 0) Voltage, DQ, DQS and DM signals.

VIL(AC)

VREF - 0.31

V

2

Input Differential Voltage, CK and CK inputs

VID(AC)

0.7

VDDQ+0.6

V

3

Input Crossing Point Voltage, CK and CK inputs

VIX(AC)

0.5*VDDQ-0.2

0.5*VDDQ+0.2

V

4

AC CHARACTERISTICS

-5B

-5

-6

-7

PARAMETER

SYM-

BOL

MIN

MAX

MIN

MAX

MIN

MAX

MIN

MAX

UNIT

SNOTES

Access window of DQs from CK/CK

tAC

-0.65

0.65

-0.65

0.65

-0.7

0.7

-0.75

0.75

ns

CK high-level width

tCH

0.45

0.55

0.45

0.55

0.45

0.55

0.45

0.55

tCK

30

CK low-level width

tCL

0.45

0.55

0.45

0.55

0.45

0.55

0.45

0.55

tCK

30

Clock cycle time

CL = 3

tCK (3)

5

10510

-

12

-

12

ns

52

CL = 2.5

tCK (2.5)

5

10610612

7

12

ns

52

CL = 2

tCK (2)

7.5

10

7.5

10

7.5

12

7.5

12

ns

52

DQ and DM input hold time relative to

DQS

tDH

0.40

0.45

0.5

ns

26,31

DQ and DM input setup time relative to

DQS

tDS

0.40

0.45

0.5

ns

26,31

DQ and DM input pulse width (for each in-

put)

tDIPW

1.75

ns

31

Access window of DQS from CK/CK

tDQSCK

-0.6

0.6

-0.6

0.6

-0.6

0.6

-0.75

0.75

ns

DQS input high pulse width

tDQSH

0.35

tCK

DQS input low pulse width

tDQSL

0.35

tCK

DQS-DQ skew, DQS to last DQ valid,

per group, per access

tDQSQ

0.40

0.45

0.5

ns

25,26

Write command to first DQS latching tran-

sition

tDQSS

0.72

1.25

0.72

1.25

0.75

1.25

0.75

1.25

tCK

DQS falling edge to CK rising - setup time

tDSS

0.2

tCK

DQS falling edge from CK rising - hold

time

tDSH

0.2

tCK

相关PDF资料 |

PDF描述 |

|---|---|

| V58C2256164SBLJ5B | 16M X 16 DDR DRAM, 0.65 ns, PBGA60 |

| V58C2256404SCLS7I | 64M X 4 DDR DRAM, 0.75 ns, PBGA60 |

| V58C2256404SHUT6E | 64M X 4 DDR DRAM, PDSO66 |

| V58C2256804SHLJ5E | 32M X 8 DDR DRAM, PBGA60 |

| V58C2256804SHUE6E | 32M X 8 DDR DRAM, PDSO66 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| V58C2256804S | 制造商:MOSEL 制造商全称:MOSEL 功能描述:HIGH PERFORMANCE 2.5 VOLT 256 Mbit DDR SDRAM |

| V58C2256804SAT-5 | 制造商:Mosel Vitelic Corporation 功能描述:SDRAM, DDR, 32M x 8, 66 Pin, Plastic, TSSOP |

| V58C265164S | 制造商:MOSEL 制造商全称:MOSEL 功能描述:64 Mbit DDR SDRAM 2.5 VOLT 4M X 16 |

| V58C265404S | 制造商:MOSEL 制造商全称:MOSEL 功能描述:HIGH PERFORMANCE 2.5 VOLT 16M X 4 DDR SDRAM 4 BANKS X 4Mbit X 4 |

| V58C265804S | 制造商:MOSEL 制造商全称:MOSEL 功能描述:HIGH PERFORMANCE 2.5 VOLT 8M X 8 DDR SDRAM 4 BANKS X 2Mbit X 8 |

发布紧急采购,3分钟左右您将得到回复。