- 您现在的位置:买卖IC网 > PDF目录16113 > VTERB-BLK-E2-U4 (Lattice Semiconductor Corporation)IP CORE VITERBI DECODER EC/ECP PDF资料下载

参数资料

| 型号: | VTERB-BLK-E2-U4 |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 7/34页 |

| 文件大小: | 0K |

| 描述: | IP CORE VITERBI DECODER EC/ECP |

| 标准包装: | 1 |

| 系列: | * |

| 其它名称: | VTERBBLKE2U4 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

�� �

�

Chapter� 2:�

�Functional� Description�

�This� chapter� provides� a� functional� description� of� the� Block� Viterbi� Decoder� IP� core.�

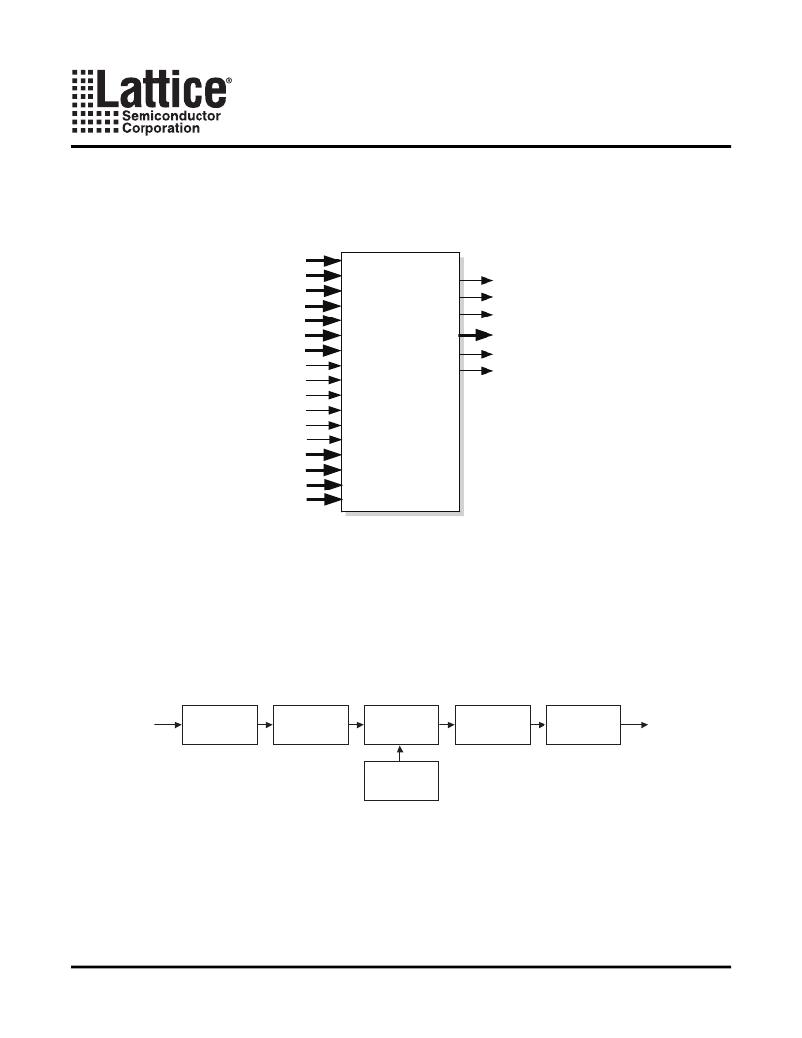

�Figure� 2-1� shows� the� interface� diagram� for� Block� Viterbi� Decoder.� The� diagram� shows� all� of� the� available� ports� for�

�the� IP.� It� should� be� noted� that� not� all� the� I/O� ports� are� available� for� all� configurations.�

�Figure� 2-1.� Block� Viterbi� Decoder� Interface� Diagram�

�din0�

�din1�

�din2�

�din3�

�din4�

�din5�

�din6�

�dout�

�outvalid�

�obvalid�

�ber�

�bervalid�

�clk�

�rstn�

�pbstart�

�Block�

�Viterbi� Decoder�

�rfib�

�ibstart�

�ibend�

�ppset�

�inrate�

�outrate�

�pp0�

�pp1�

�General� Description�

�Viterbi� decoding� is� an� efficient� algorithm� for� decoding� convolutionally� encoded� sequences� corrupted� by� channel�

�noise� back� to� the� original� sequence.� A� digital� transmit-receive� system� shown� in� Figure� 2-2� uses� a� Viterbi� decoder�

�for� decoding� the� convolutionally� encoded� data.� The� digital� data� stream� (e.g.,� voice,� image,� or� any� packetized� data)�

�is� encoded,� modulated,� and� transmitted� through� a� wired� or� wireless� channel.� A� “noise”� block� connected� to� the�

�channel� symbolically� denotes� the� channel� noise.� The� data� received� from� the� channel� at� the� receiver� side� is� first�

�demodulated� and� then� decoded� using� the� Viterbi� decoder.� The� decoded� output� is� equivalent� to� the� transmitted� dig-�

�ital� data� stream.�

�Figure� 2-2.� Digital� Transmit-Receive� System�

�Transmitted�

�Data� Stream�

�Convolutional�

�Encoder�

�Modulator�

�Channel�

�Demodulator�

�Block� Viterbi�

�Decoder�

�Received�

�Data� Stream�

�Noise�

�Convolutional� Encoding�

�Figure� 2-3� shows� an� example� of� convolutional� encoding.� In� this� example,� each� input� symbol� has� two� corresponding�

�output� symbols;� hence� the� encoding� is� called� 1/2� rate� convolutional� encoding.� To� generate� the� output,� the� encoder�

�uses� seven� values� of� the� input� signal,� one� present� and� six� past.� The� set� of� past� values� of� input� data� is� called� the�

�“state”� of� the� encoder.� The� number� of� input� data� values� used� to� generate� the� code� is� called� the� constraint� length�

�(K).� In� this� case,� the� constraint� length� is� 7.� Each� set� of� outputs� is� generated� by� XOR-ing� a� pattern� of� current� and�

�shifted� values� of� input� data.� The� patterns� used� to� generate� the� coded� output� value� can� be� expressed� as� binary�

�strings� called� generator� polynomials� (GP).� In� this� example,� the� generator� polynomials� are� 171� and� 133� (in� octal).�

�IPUG32_02.7,� June� 2010�

�7�

�Block� Viterbi� Decoder� User’s� Guide�

�相关PDF资料 |

PDF描述 |

|---|---|

| 50ZLJ100MT78X11.5 | CAP ALUM 100UF 50V 20% RADIAL |

| M3BRK-3406R | IDC CABLE - MSR34K/MC34M/MPR34K |

| M3URK-2620K | IDC CABLE - MKS26K/MC26F/MPR26K |

| 10ZLH1000M8X16 | CAP ALUM 1000UF 10V 20% RADIAL |

| M3UYK-2620K | IDC CABLE - MKS26K/MC26F/MPD26K |

相关代理商/技术参数 |

参数描述 |

|---|---|

| VTERB-BLK-E3-U4 | 功能描述:开发软件 Block Viterbi Decoder RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| VTERB-BLK-E3-UT4 | 功能描述:开发软件 BLOCK VITERBI DECODER (ECP3) RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| VTERB-BLK-P2-U4 | 功能描述:编码器、解码器、复用器和解复用器 Block Viterbi Decoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray |

| VTERB-BLK-PM-U4 | 功能描述:开发软件 Blck Viterbi Decodr User Config RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| VTERB-BLK-SC-U4 | 功能描述:编码器、解码器、复用器和解复用器 Block Viterbi Decoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。