- 您现在的位置:买卖IC网 > PDF目录16113 > VTERB-BLK-E2-U4 (Lattice Semiconductor Corporation)IP CORE VITERBI DECODER EC/ECP PDF资料下载

参数资料

| 型号: | VTERB-BLK-E2-U4 |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 9/34页 |

| 文件大小: | 0K |

| 描述: | IP CORE VITERBI DECODER EC/ECP |

| 标准包装: | 1 |

| 系列: | * |

| 其它名称: | VTERBBLKE2U4 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

�� �

�

Lattice� Semiconductor�

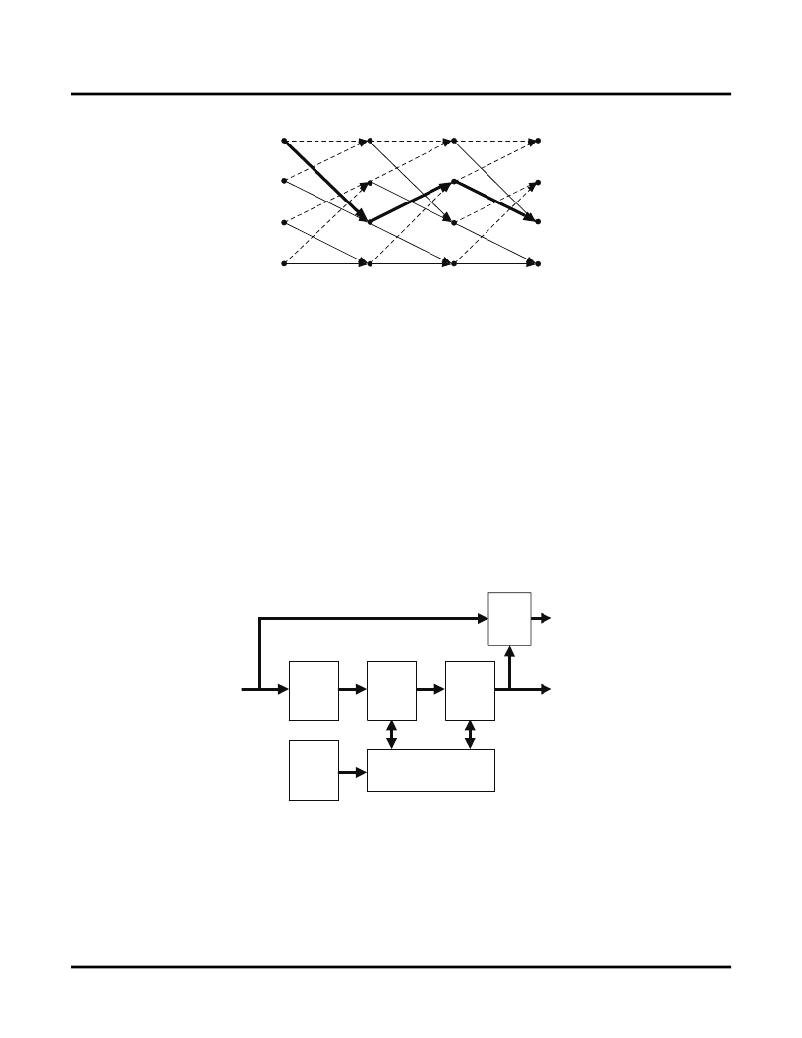

�Figure� 2-5.� Trellis� Tree�

�Functional� Description�

�00�

�01�

�10�

�11�

�0/00�

�1/00�

�0/01�

�1/01�

�0/10�

�1/10�

�0/11�

�1/11�

�0/00�

�1/00�

�0/01�

�1/01�

�0/10�

�1/10�

�0/11�

�1/11�

�0/00�

�1/00�

�0/01�

�1/01�

�0/10�

�1/10�

�0/11�

�1/11�

�Trellis� for� 3� stages� and� constraint� length� =� 3�

�Branches� corresponding� to� input� seq.� 101� is� highlighted�

�In� the� above� trellis,� the� branches� for� three� transitions� are� drawn.� The� path� of� the� trellis� for� a� typical� input� sequence,�

�101,� is� highlighted� in� the� figure.� Any� transmission� error� alters� the� path� traversed� in� the� trellis.� In� Viterbi� decoding,�

�such� a� trellis� is� formed� in� memory,� where� the� metrics� corresponding� to� all� paths� are� recorded.� After� constructing�

�the� trellis� for� a� sufficient� length� (called� the� traceback� length,� L),� the� traceback� process� starts� from� node� 0� in� the� last�

�state.� During� the� traceback� process,� the� original� sequence� is� reconstructed� from� the� trellis.� In� error-prone� applica-�

�tions,� however,� a� trellis� of� length� 2L� is� constructed� and� two� traceback� processes� are� employed.� The� first� traceback�

�starts� from� node� 0,� traces� back� L� stages� of� the� trellis,� and� ends� up� in� a� node� which� is� more� likely� to� be� the� right�

�starting� point� for� the� second� traceback.� The� second� traceback� starts� from� this� reliable� starting� point� and� traces�

�back� another� L� nodes.� The� data� corresponding� to� the� second� traceback� are� decoded� to� result� in� the� original� data�

�stream.�

�Functional� Description�

�A� simplified� implementation� of� the� Lattice� Block� Viterbi� Decoder� IP� is� shown� in� Figure� 2-6� .� A� brief� description� of� the�

�modules� is� given� below.�

�Figure� 2-6.� Internal� Architecture� of� the� Viterbi� Decoder�

�BER�

�BER�

�din�

�BMU�

�ACS�

�TBU�

�dout�

�MMU�

�MEM�

�Branch� Metric� Unit� (BMU)�

�This� module� takes� in� the� input� data� from� the� channel� and� computes� a� metric� for� each� state� and� input� combination.�

�The� metric� is� the� Hamming� distance� for� hard-decision� encoded� data� and� l1� norm� (sum� of� absolute� values)� for� soft�

�decision� encoded� data.� The� BMU� also� includes� a� depuncturing� unit� for� punctured� codes.� This� module� has� three�

�major� sub-modules:� state� encoder,� metric� computer,� and� de-puncture� unit.�

�IPUG32_02.7,� June� 2010�

�9�

�Block� Viterbi� Decoder� User’s� Guide�

�相关PDF资料 |

PDF描述 |

|---|---|

| 50ZLJ100MT78X11.5 | CAP ALUM 100UF 50V 20% RADIAL |

| M3BRK-3406R | IDC CABLE - MSR34K/MC34M/MPR34K |

| M3URK-2620K | IDC CABLE - MKS26K/MC26F/MPR26K |

| 10ZLH1000M8X16 | CAP ALUM 1000UF 10V 20% RADIAL |

| M3UYK-2620K | IDC CABLE - MKS26K/MC26F/MPD26K |

相关代理商/技术参数 |

参数描述 |

|---|---|

| VTERB-BLK-E3-U4 | 功能描述:开发软件 Block Viterbi Decoder RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| VTERB-BLK-E3-UT4 | 功能描述:开发软件 BLOCK VITERBI DECODER (ECP3) RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| VTERB-BLK-P2-U4 | 功能描述:编码器、解码器、复用器和解复用器 Block Viterbi Decoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray |

| VTERB-BLK-PM-U4 | 功能描述:开发软件 Blck Viterbi Decodr User Config RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| VTERB-BLK-SC-U4 | 功能描述:编码器、解码器、复用器和解复用器 Block Viterbi Decoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。