- 您现在的位置:买卖IC网 > PDF目录68583 > WJLXT384LEB1 (INTEL CORP) DATACOM, PCM TRANSCEIVER, PQFP144 PDF资料下载

参数资料

| 型号: | WJLXT384LEB1 |

| 厂商: | INTEL CORP |

| 元件分类: | 数字传输电路 |

| 英文描述: | DATACOM, PCM TRANSCEIVER, PQFP144 |

| 封装: | 20 X 20MM, ROHS COMPLIANT, LQFP-144 |

| 文件页数: | 123/140页 |

| 文件大小: | 1514K |

| 代理商: | WJLXT384LEB1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页当前第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页

83

Document Number: 248994

Revision Number: 005

Revision Date: November 28, 2005

Intel LXT384 Octal T1/E1/J1 S/H PCM Transceiver with JA

Table 43. Global Control Register, GCR - 0Fh

Bit

Name

Description

R/W

7

-

Reserved.

R/W

6

RAISEN

Receive Alarm Indication Signal Enable.

This bit controls automatic AIS insertion in the receive path when LOS occurs.

0 = Receive path AIS insertion is disabled on LOS.

1 = Receive path AIS insertion is enabled on LOS, and the effective output

appears on RPOS/RNEG.

NOTE: This feature is not available in data-recovery mode (that is, when

MCLK is high). When changing the value of the RAISEN bit, disable

AIS interrupts to prevent inadvertent interrupts.

R/W

5

CDIS

Circuit Disable.

This bit enables/disables the short-circuit protection feature for the transmitters.

0 = Enable

1 = Disable

R/W

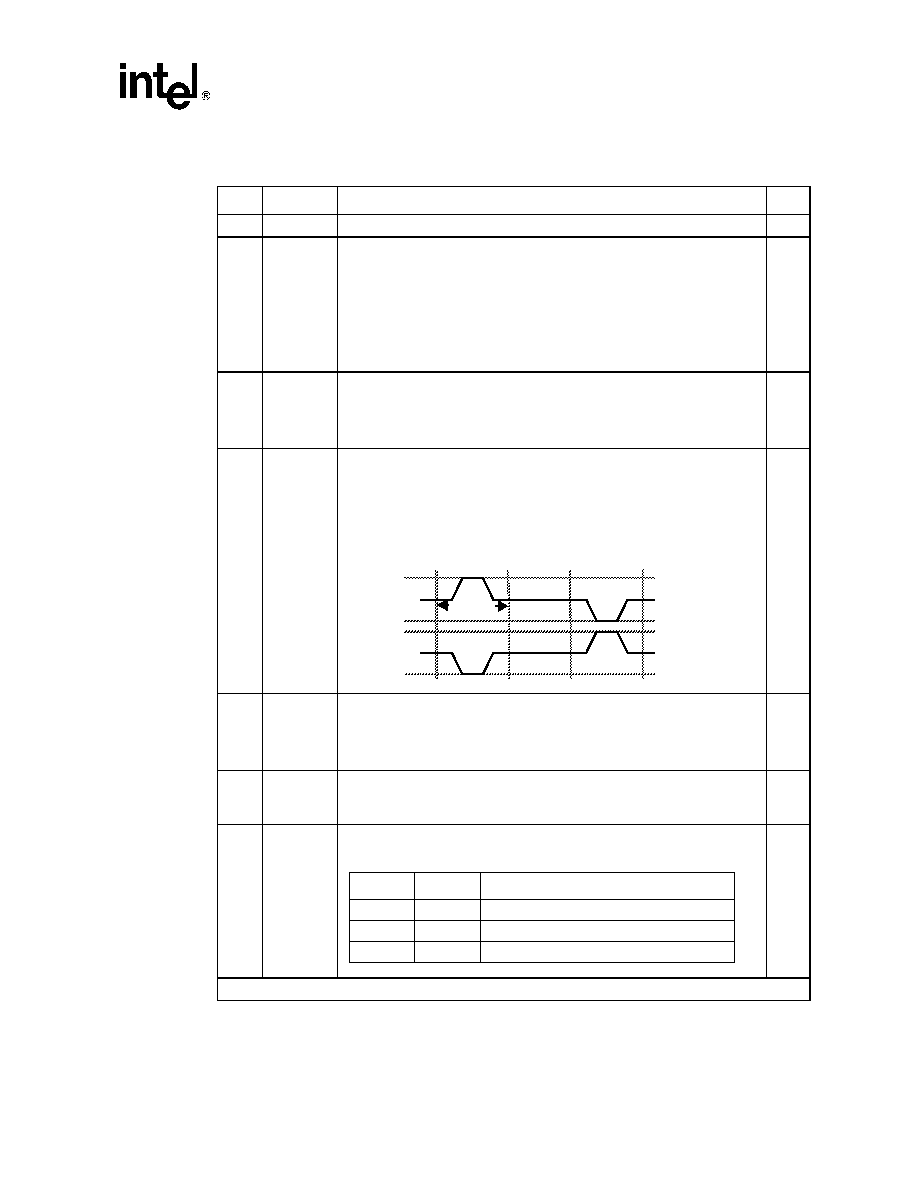

4CODEN

Code Enable.

This bit selects one of two available zero-suppression codes. Zero suppression

operations are available only with unipolar I/O.

0 = High-Density Bipolar three (HDB3) for E1 or B8ZS for T1

1 = Alternate Mark Inversion, or ‘AMI’. The following figure shows AMI

coding that is 1:1 (or ‘50%’), indicating that for every one bit sit to a ‘1’,

there is a corresponding ‘0’ logic state.

R/W

3FIFO64

First-In First-Out 64-Bit Select.

This bit determines the jitter attenuator FIFO depth as follows:

0 = Jitter attenuator FIFO is 32 bits deep.

1 = Jitter attenuator FIFO is 64 bits deep.

R/W

2JACF

Jitter Attenuator Corner Frequency.

This bit determines the jitter attenuator low-limit 3-dB corner frequency. For

more information, see Chapter 14.0, “Jitter Performance”.

R/W

1:0

JASEL1:0

Jitter Attenuator Select.

These bits determine the jitter attenuator position as follows:

R/W

1. On power-on reset, the register is set to ‘0’.

TTIP

TRING

1

0

1

Bit Cell

JASEL1

JASEL0

Jitter Attenuator Position

x

0

Jitter attenuator is disabled.

0

1

Jitter attenuator position is the transmit path.

1

Jitter attenuator position is the receive path.

相关PDF资料 |

PDF描述 |

|---|---|

| WJLXT384LEB1 | DATACOM, PCM TRANSCEIVER, PQFP144 |

| WJLXT385LEB1 | DATACOM, PCM TRANSCEIVER, PQFP144 |

| WJLXT385LEB1 | DATACOM, PCM TRANSCEIVER, PQFP144 |

| WJLXT386LEB2 | DATACOM, PCM TRANSCEIVER, PQFP100 |

| WJLXT386LEB2 | DATACOM, PCM TRANSCEIVER, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| WJLXT386LE.B2 | 功能描述:IC TRANS QUAD T1/E1/J1 100-LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:25 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:4.5 V ~ 5.5 V 安装类型:通孔 封装/外壳:16-DIP(0.300",7.62mm) 供应商设备封装:16-PDIP 包装:管件 |

| WJLXT6155LE.B5 | 制造商:Intel 功能描述:SONET/SDH/ATM Transceiver 1TX 1RX 64-Pin LQFP |

| WJLXT6155LE.B5-866255 | 功能描述:TXRX SDH/SONET/ATM HS 64-LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:50 系列:- 类型:收发器 驱动器/接收器数:1/1 规程:RS422,RS485 电源电压:4.75 V ~ 5.25 V 安装类型:通孔 封装/外壳:8-DIP(0.300",7.62mm) 供应商设备封装:8-PDIP 包装:管件 产品目录页面:1402 (CN2011-ZH PDF) |

| WJLXT6155LE.B5-866256 | 制造商:Cortina Systems Inc 功能描述:SONET/SDH/ATM Transceiver 1TX 1RX 64-Pin LQFP T/R |

| WJLXT901ALC.A4 | 功能描述:IC 10BASE-T/AUI TXCVR 64-LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:1,000 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-SOIC(0.295",7.50mm 宽) 供应商设备封装:16-SOIC 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。