- 您现在的位置:买卖IC网 > PDF目录376449 > X98021L128-3.3-Z (INTERSIL CORP) 210MHz Triple Video Digitizer with Digital PLL PDF资料下载

参数资料

| 型号: | X98021L128-3.3-Z |

| 厂商: | INTERSIL CORP |

| 元件分类: | 消费家电 |

| 英文描述: | 210MHz Triple Video Digitizer with Digital PLL |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP128 |

| 封装: | 14 X 20 MM, ROHS COMPLIANT, MS-022, MQFP-128 |

| 文件页数: | 9/29页 |

| 文件大小: | 294K |

| 代理商: | X98021L128-3.3-Z |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

9

FN8219.0

June 2, 2005

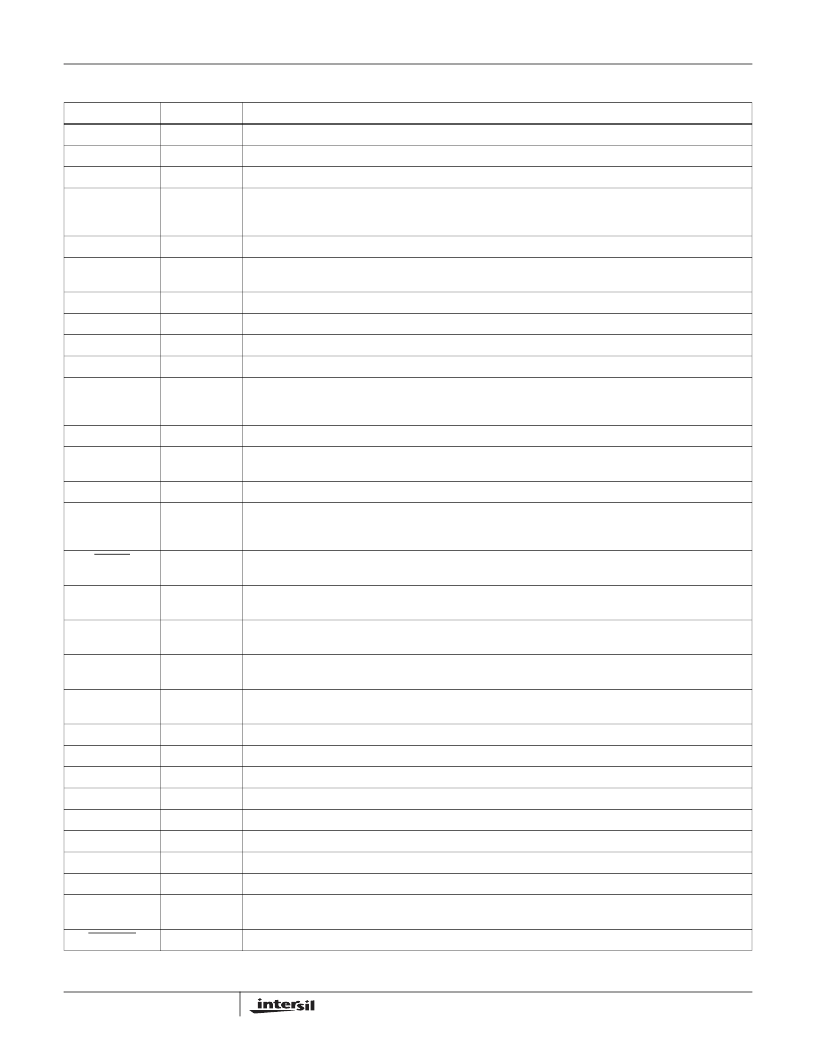

Pin Descriptions

SYMBOL

PIN

DESCRIPTION

R

IN

1

7

Analog input. Red channel 1. DC couple or AC couple through 0.1μF.

G

IN

1

12

Analog input. Green channel 1. DC couple or AC couple through 0.1μF.

B

IN

1

19

Analog input. Blue channel 1. DC couple or AC couple through 0.1μF.

RGB

GND

1

13

Analog input. Ground reference for the R, G, and B inputs of channel 1 in the DC coupled configuration.

Connect to the same ground as channel 1's R, G, and B termination resistors. This signal is not used in the

AC-coupled configuration, but the pin should still be tied to GND

A

.

SOG

IN

1

14

Analog input. Sync on Green. Connect to G

IN

1 through a 0.01μF capacitor in series with a 500

Ω

resistor.

HSYNC

IN

1

33

Digital input, 5V tolerant, 240mV hysteresis, 1.2k

Ω

impedance to GND

A

. Connect to channel 1's HSYNC

signal through a 680

Ω

series resistor.

VSYNC

IN

1

44

Digital input, 5V tolerant, 500mV hysteresis. Connect to channel 1's VSYNC signal.

R

IN

2

22

Analog input. Red channel 2. DC couple or AC couple through 0.1μF.

G

IN

2

24

Analog input. Green channel 2. DC couple or AC couple through 0.1μF.

B

IN

2

28

Analog input. Blue channel 2. DC couple or AC couple through 0.1μF.

RGB

GND

2

25

Analog input. Ground reference for the R, G, and B inputs of channel 2 in the DC coupled configuration.

Connect to the same ground as channel 1's R, G, and B termination resistors. This signal is not used in the

AC-coupled configuration, but the pin should still be tied to GND

A

.

SOG

IN

2

26

Analog input. Sync on Green. Connect to G

IN

1 through a 0.01μF capacitor in series with a 500

Ω

resistor.

HSYNC

IN

2

34

Digital input, 5V tolerant, 240mV hysteresis, 1.2k

Ω

impedance to GND

A

. Connect to channel 2's HSYNC

signal through a 680

Ω

series resistor.

VSYNC

IN

2

45

Digital input, 5V tolerant, 500mV hysteresis. Connect to channel 2's VSYNC signal.

CLOCKINV

IN

41

Digital input, 5V tolerant. When high, changes the pixel sampling phase by 180 degrees. Toggle at frame

rate during VSYNC to allow 2x undersampling to sample odd and even pixels on sequential frames. Tie to

D

GND

if unused.

RESET

46

Digital input, 5V tolerant, active low, 70k

Ω

pull-up to V

D

. Take low for at least 1μs and then high again to

reset the X98021. This pin is not necessary for normal use and may be tied directly to the V

D

supply.

XTAL

IN

39

Analog input. Connect to external 23MHz to 27MHz crystal and load capacitor (see crystal spec for

recommended loading). Typical oscillation amplitude is 1.0V

P-P

centered around 0.5V.

XTAL

OUT

40

Analog output. Connect to external 23MHz to 27MHz crystal and load capacitor (see crystal spec for

recommended loading). Typical oscillation amplitude is 1.0V

P-P

centered around 0.5V.

XTALCLK

OUT

47

3.3V digital output. Buffered crystal clock output at f

XTAL

or f

XTAL

/2. May be used as system clock for other

system components.

SADDR

48

Digital input, 5V tolerant. Address = 0x4C (0x98 including R/W bit) when tied low. Address = 0x4D (0x9A

including R/W bit) when tied high.

SCL

50

Digital input, 5V tolerant, 500mV hysteresis. Serial data clock for 2-wire interface.

SDA

49

Bidirectional Digital I/O, open drain, 5V tolerant. Serial data I/O for 2-wire interface.

R

P

[7:0]

112-119

3.3V digital output. Red channel, primary pixel data. 58K pulldown when three-stated.

R

S

[7:0]

100-107

3.3V digital output. Red channel, secondary pixel data. 58K pulldown when three-stated.

G

P

[7:0]

90-97

3.3V digital output. Green channel, primary pixel data. 58K pulldown when three-stated.

G

S

[7:0]

80-87

3.3V digital output. Green channel, secondary pixel data. 58K pulldown when three-stated.

B

P

[7:0]

68-75

3.3V digital output. Blue channel, primary pixel data. 58K pulldown when three-stated.

B

S

[7:0]

55-62

3.3V digital output. Blue channel, secondary pixel data. 58K pulldown when three-stated.

DATACLK

121

3.3V digital output. Data clock output. Equal to pixel clock rate in 24 bit mode, one half pixel clock rate in 48

bit mode.

DATACLK

122

3.3V digital output. Inverse of DATACLK.

X98021

相关PDF资料 |

PDF描述 |

|---|---|

| X98024 | 240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3 | 240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3-Z | 240MHz Triple Video Digitizer with Digital PLL |

| XC145481 | 3 V PCM Codec-Filter |

| XC145481DW | 3 V PCM Codec-Filter |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X98024 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:240MHz Triple Video Digitizer with Digital PLL |

| X98024_06 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3-Z | 功能描述:IC TRPL VID DIGITIZER 128MQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 视频处理 系列:- 标准包装:250 系列:- 类型:电平移位器 应用:LCD 电视机/监控器 安装类型:表面贴装 封装/外壳:28-WFQFN 裸露焊盘 供应商设备封装:28-WQFN(4x4)裸露焊盘 包装:带卷 (TR) 其它名称:296-32523-2TPS65198RUYT-ND |

| X98027 | 制造商:XICOR 制造商全称:Xicor Inc. 功能描述:PRELIMINARY INFORMATION |

发布紧急采购,3分钟左右您将得到回复。