参数资料

| 型号: | XC2S50E-6FTG256I |

| 厂商: | Xilinx Inc |

| 文件页数: | 27/108页 |

| 文件大小: | 0K |

| 描述: | IC SPARTAN-IIE FPGA 50K 256FTBGA |

| 产品变化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 标准包装: | 90 |

| 系列: | Spartan®-IIE |

| LAB/CLB数: | 384 |

| 逻辑元件/单元数: | 1728 |

| RAM 位总计: | 32768 |

| 输入/输出数: | 182 |

| 门数: | 50000 |

| 电源电压: | 1.71 V ~ 1.89 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 256-LBGA |

| 供应商设备封装: | 256-FTBGA |

| 其它名称: | 122-1329 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页

DS077-2 (v3.0) August 9, 2013

25

Product Specification

Spartan-IIE FPGA Family: Functional Description

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

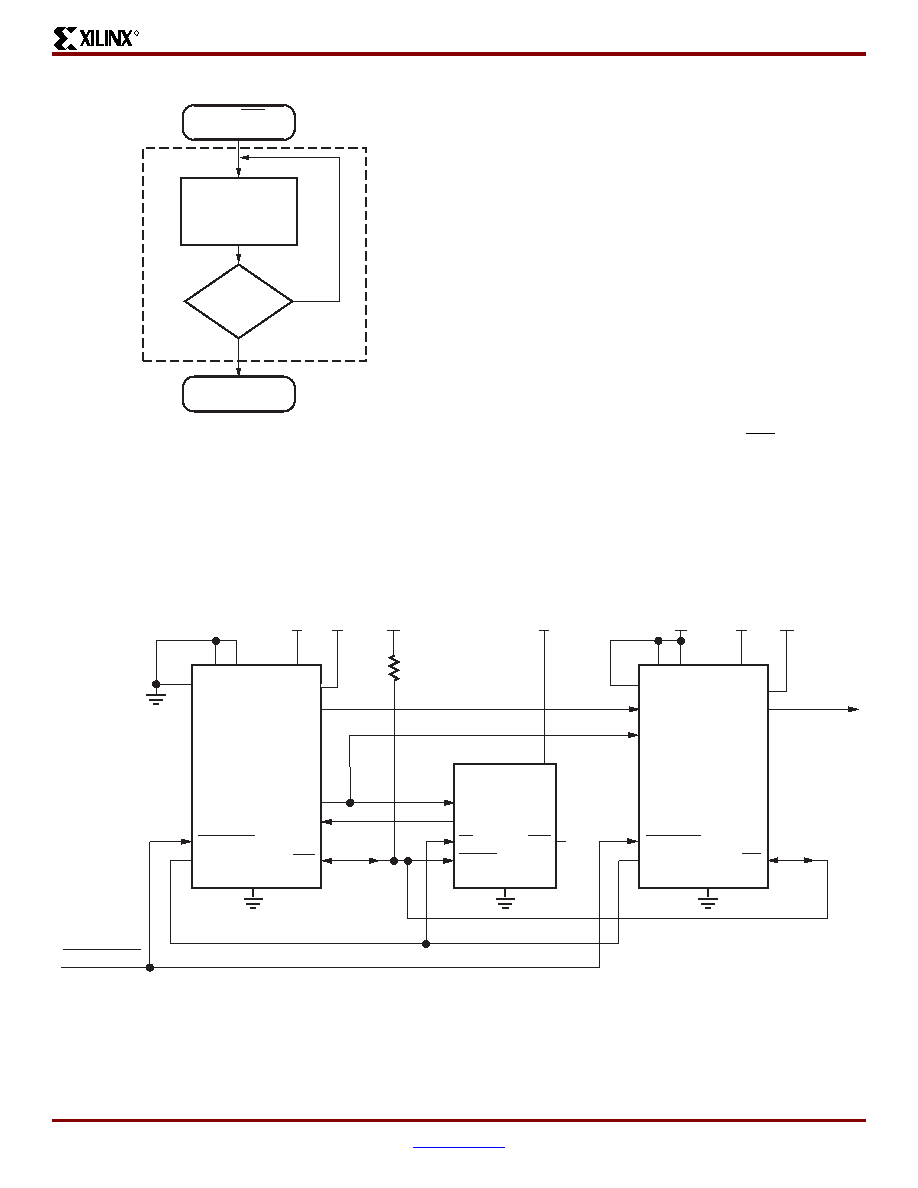

Slave Serial Mode

In Slave Serial mode, the FPGA’s CCLK pin is driven by an

external source, allowing the FPGA to be configured from

other logic devices such as microprocessors or in a

daisy-chain configuration. Figure 19 shows connections for

a Master Serial FPGA configuring a Slave Serial FPGA

from a PROM. A Spartan-IIE device in slave serial mode

should be connected as shown for the third device from the

left. Slave Serial mode is selected by a <11x> on the mode

pins (M0, M1, M2). The weak pull-ups on the mode pins

make slave serial the default mode if the pins are left uncon-

nected.

The serial bitstream must be setup at the DIN input pin a

short time before each rising edge of an externally gener-

ated CCLK.

Timing for Slave Serial mode is shown in Figure 24,

Daisy Chain

Multiple FPGAs in Slave Serial mode can be daisy-chained

for configuration from a single source. After an FPGA is

configured, data for the next device is sent to the DOUT pin.

Data on the DOUT pin changes on the rising edge of CCLK.

Note that DOUT changes on the falling edge of CCLK for

some Xilinx families but mixed daisy chains are allowed.

Configuration must be delayed until INIT pins of all

daisy-chained FPGAs are High. For more information, see

The maximum amount of data that can be sent to the DOUT

pin for a serial daisy chain is 220-1 (1,048,575) 32-bit words,

or 33,554,400 bits, which is approximately 8 XC2S600E bit-

streams. The configuration bitstream of downstream

devices is limited to this size.

Figure 18: Loading Serial Mode Configuration Data

No

Yes

End of

Configuration

Data File?

After INIT

Goes High

User Load One

Configuration

Bit on Next

CCLK Rising Edge

To CRC Check

DS001_14_032300

Notes:

1.

If the DriveDone configuration option is not active for any of the FPGAs, pull up DONE with a 330

Ω resistor.

Figure 19: Master/Slave Serial Configuration Circuit Diagram

Spartan-IIE

(Master Serial)

Xilinx

PROM

PROGRAM

M2

M0 M1

DOUT

CCLK

CLK

3.3V

DATA

CE

CEO

RESET/OE

DIN

INIT

DONE

PROGRAM

3.3 K

DS077-2_04_061708

GND

VCC

3.3V

VCCO

VCCINT

1.8V

3.3V

1.8V

Spartan-IIE

(Slave)

DONE

INIT

PROGRAM

CCLK

DIN

DOUT

M2

M0 M1

GND

VCCO

VCCINT

相关PDF资料 |

PDF描述 |

|---|---|

| EHHD15MFB | CONN DSUB 15PIN MALE-FMALE BLK |

| 24LCS52T-I/MC | IC EEPROM 2KBIT 400KHZ 8DFN |

| XC2S100-6PQ208C | IC FPGA 2.5V C-TEMP 208-PQFP |

| ACC60DREI | CONN EDGECARD 120PS .100 EYELET |

| XC2S100-5PQ208I | IC FPGA 2.5V I-TEMP 208-PQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC2S50E-6PQ208C | 功能描述:IC FPGA 1.8V 384 CLB'S 208-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-IIE 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XC2S50E-6PQ208I | 制造商:Xilinx 功能描述:IC SPARTAN-IIE FPGA 50K 208-PQFP 制造商:Xilinx 功能描述:IC FPGA 146 I/O 208PQFP |

| XC2S50E-6PQG208C | 功能描述:IC SPARTAN-IIE FPGA 50K 208-PQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-IIE 标准包装:24 系列:ECP2 LAB/CLB数:1500 逻辑元件/单元数:12000 RAM 位总计:226304 输入/输出数:131 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) |

| XC2S50E-6PQG208I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S50E-6TQ144C | 功能描述:IC FPGA 1.8V 384 CLB'S 144-TQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-IIE 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

发布紧急采购,3分钟左右您将得到回复。