参数资料

| 型号: | XC2S50E-6FTG256I |

| 厂商: | Xilinx Inc |

| 文件页数: | 32/108页 |

| 文件大小: | 0K |

| 描述: | IC SPARTAN-IIE FPGA 50K 256FTBGA |

| 产品变化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 标准包装: | 90 |

| 系列: | Spartan®-IIE |

| LAB/CLB数: | 384 |

| 逻辑元件/单元数: | 1728 |

| RAM 位总计: | 32768 |

| 输入/输出数: | 182 |

| 门数: | 50000 |

| 电源电压: | 1.71 V ~ 1.89 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 256-LBGA |

| 供应商设备封装: | 256-FTBGA |

| 其它名称: | 122-1329 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页

DS077-1 (v3.0) August 9, 2013

3

Product Specification

2001–2013 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other

trademarks are the property of their respective owners.

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

Introduction

The Spartan-IIE Field-Programmable Gate Array family

gives users high performance, abundant logic resources,

and a rich feature set, all at an exceptionally low price. The

seven-member family offers densities ranging from 50,000

to 600,000 system gates, as shown in Table 1. System per-

formance is supported beyond 200 MHz.

Features include block RAM (to 288K bits), distributed RAM

(to 221,184 bits), 19 selectable I/O standards, and four

DLLs (Delay-Locked Loops). Fast, predictable interconnect

means that successive design iterations continue to meet

timing requirements.

The Spartan-IIE family is a superior alternative to

mask-programmed ASICs. The FPGA avoids the initial cost,

lengthy

development

cycles,

and

inherent

risk

of

conventional ASICs. Also, FPGA programmability permits

design upgrades in the field with no hardware replacement

necessary (impossible with ASICs).

Features

Second generation ASIC replacement technology

-

Densities as high as 15,552 logic cells with up to

600,000 system gates

-

Streamlined features based on Virtex-E FPGA

architecture

-

Unlimited in-system reprogrammability

-

Very low cost

-

Cost-effective 0.15 micron technology

System level features

-

SelectRAM hierarchical memory:

16 bits/LUT distributed RAM

Configurable 4K-bit true dual-port block RAM

Fast interfaces to external RAM

-

Fully 3.3V PCI compliant to 64 bits at 66 MHz and

CardBus compliant

-

Low-power segmented routing architecture

-

Dedicated carry logic for high-speed arithmetic

-

Efficient multiplier support

-

Cascade chain for wide-input functions

-

Abundant registers/latches with enable, set, reset

-

Four dedicated DLLs for advanced clock control

Eliminate clock distribution delay

Multiply, divide, or phase shift

-

Four primary low-skew global clock distribution nets

-

IEEE 1149.1 compatible boundary scan logic

Versatile I/O and packaging

-

Pb-free package options

-

Low-cost packages available in all densities

-

Family footprint compatibility in common packages

-

19 high-performance interface standards

LVTTL, LVCMOS, HSTL, SSTL, AGP, CTT, GTL

LVDS and LVPECL differential I/O

-

Up to 205 differential I/O pairs that can be input,

output, or bidirectional

-

Hot swap I/O (CompactPCI friendly)

Core logic powered at 1.8V and I/Os powered at 1.5V,

2.5V, or 3.3V

Fully supported by powerful Xilinx ISE development

system

-

Fully automatic mapping, placement, and routing

-

Integrated with design entry and verification tools

-

Extensive IP library including DSP functions and

soft processors

Spartan-IIE FPGA Family:

Introduction and Ordering

Information

DS077-1 (v3.0) August 9, 2013

0

Product Specification

R

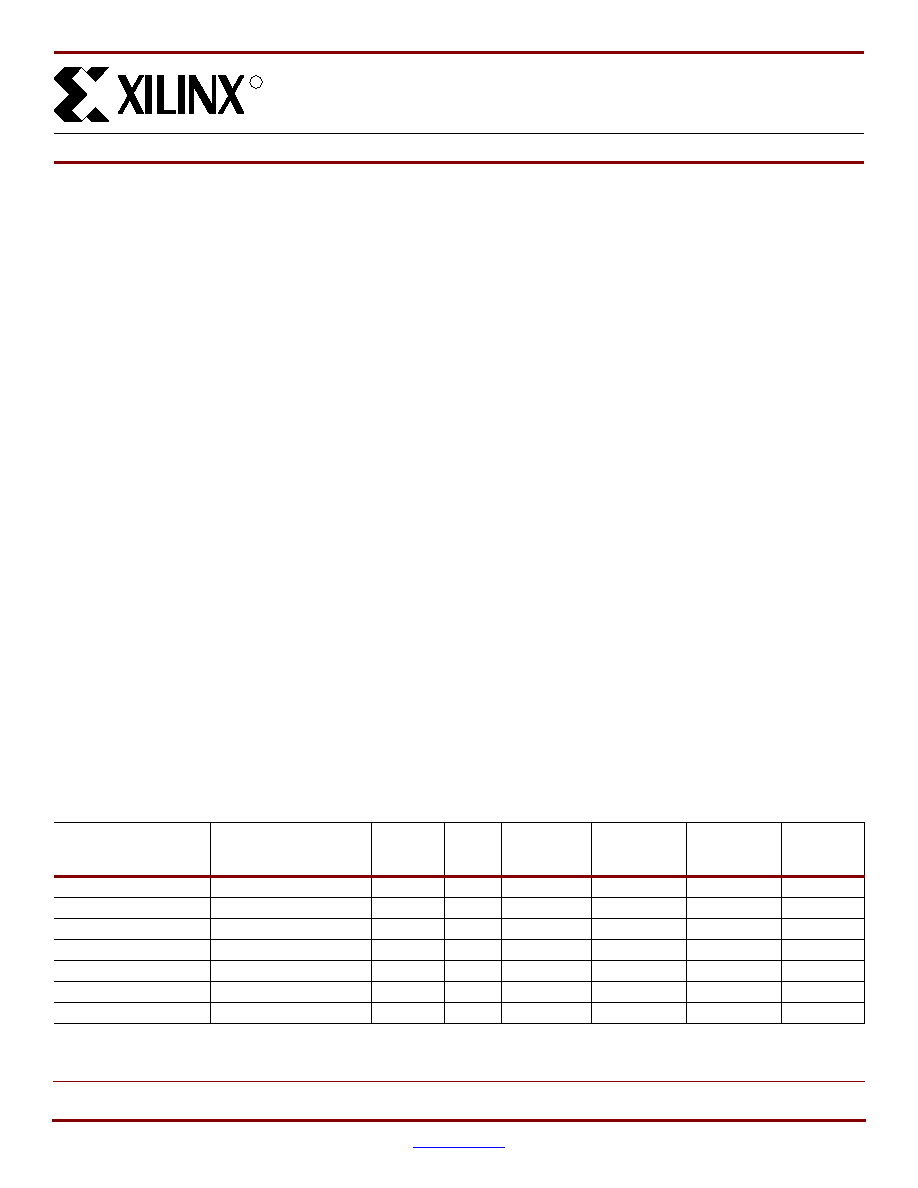

Table 1: Spartan-IIE FPGA Family Members

Device

Logic

Cells

Typical

System Gate Range

(Logic and RAM)

CLB

Array

(R x C)

Total

CLBs

Maximum

Available

User I/O(1)

Maximum

Differential

I/O Pairs

Distributed

RAM Bits

Block RAM

Bits

XC2S50E

1,728

23,000 - 50,000

16 x 24

384

182

83

24,576

32K

XC2S100E

2,700

37,000 - 100,000

20 x 30

600

202

86

38,400

40K

XC2S150E

3,888

52,000 - 150,000

24 x 36

864

265

114

55,296

48K

XC2S200E

5,292

71,000 - 200,000

28 x 42

1,176

289

120

75,264

56K

XC2S300E

6,912

93,000 - 300,000

32 x 48

1,536

329

120

98,304

64K

XC2S400E

10,800

145,000 - 400,000

40 x 60

2,400

410

172

153,600

160K

XC2S600E

15,552

210,000 - 600,000

48 x 72

3,456

514

205

221,184

288K

Notes:

1.

User I/O counts include the four global clock/user input pins. See details in Table 2, page 5

相关PDF资料 |

PDF描述 |

|---|---|

| EHHD15MFB | CONN DSUB 15PIN MALE-FMALE BLK |

| 24LCS52T-I/MC | IC EEPROM 2KBIT 400KHZ 8DFN |

| XC2S100-6PQ208C | IC FPGA 2.5V C-TEMP 208-PQFP |

| ACC60DREI | CONN EDGECARD 120PS .100 EYELET |

| XC2S100-5PQ208I | IC FPGA 2.5V I-TEMP 208-PQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC2S50E-6PQ208C | 功能描述:IC FPGA 1.8V 384 CLB'S 208-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-IIE 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XC2S50E-6PQ208I | 制造商:Xilinx 功能描述:IC SPARTAN-IIE FPGA 50K 208-PQFP 制造商:Xilinx 功能描述:IC FPGA 146 I/O 208PQFP |

| XC2S50E-6PQG208C | 功能描述:IC SPARTAN-IIE FPGA 50K 208-PQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-IIE 标准包装:24 系列:ECP2 LAB/CLB数:1500 逻辑元件/单元数:12000 RAM 位总计:226304 输入/输出数:131 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) |

| XC2S50E-6PQG208I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S50E-6TQ144C | 功能描述:IC FPGA 1.8V 384 CLB'S 144-TQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-IIE 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

发布紧急采购,3分钟左右您将得到回复。