参数资料

| 型号: | XC3020A-7PC84C |

| 厂商: | Xilinx Inc |

| 文件页数: | 44/76页 |

| 文件大小: | 0K |

| 描述: | IC LOGIC CL ARRAY 2000GAT 84PLCC |

| 产品变化通告: | Product Discontinuation 27/Apr/2010 |

| 标准包装: | 1 |

| 系列: | XC3000A/L |

| LAB/CLB数: | 64 |

| RAM 位总计: | 14779 |

| 输入/输出数: | 64 |

| 门数: | 1500 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 84-LCC(J 形引线) |

| 供应商设备封装: | 84-PLCC |

| 其它名称: | 122-1010 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页当前第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

R

November 9, 1998 (Version 3.1)

7-51

XC3000 Series Field Programmable Gate Arrays

7

XC3000L IOB Switching Characteristics Guidelines

Testing of the switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100%

functionally tested. Since many internal timing parameters cannot be measured directly, they are derived from benchmark

timing patterns. The following guidelines reflect worst-case values over the recommended operating conditions. For more

detailed, more precise, and more up-to-date timing information, use the values provided by the timing calculator and used

in the simulator.

Notes: 1. Timing is measured at pin threshold, with 50 pF external capacitive loads (incl. test fixture). Typical slew rate limited output

rise/fall times are approximately four times longer.

2. Voltage levels of unused (bonded and unbonded) pads must be valid logic levels. Each can be configured with the internal

pull-up resistor or alternatively configured as a driven output or driven from an external source.

3. Input pad set-up time is specified with respect to the internal clock (ik). In order to calculate system set-up time, subtract

clock delay (pad to ik) from the input pad set-up time value. Input pad holdtime with respect to the internal clock (ik) is

negative. This means that pad level changes immediately before the internal clock edge (ik) will not be recognized.

4. TPID, TPTG, and TPICK are 3 ns higher for XTL2 when the pin is configured as a user input.

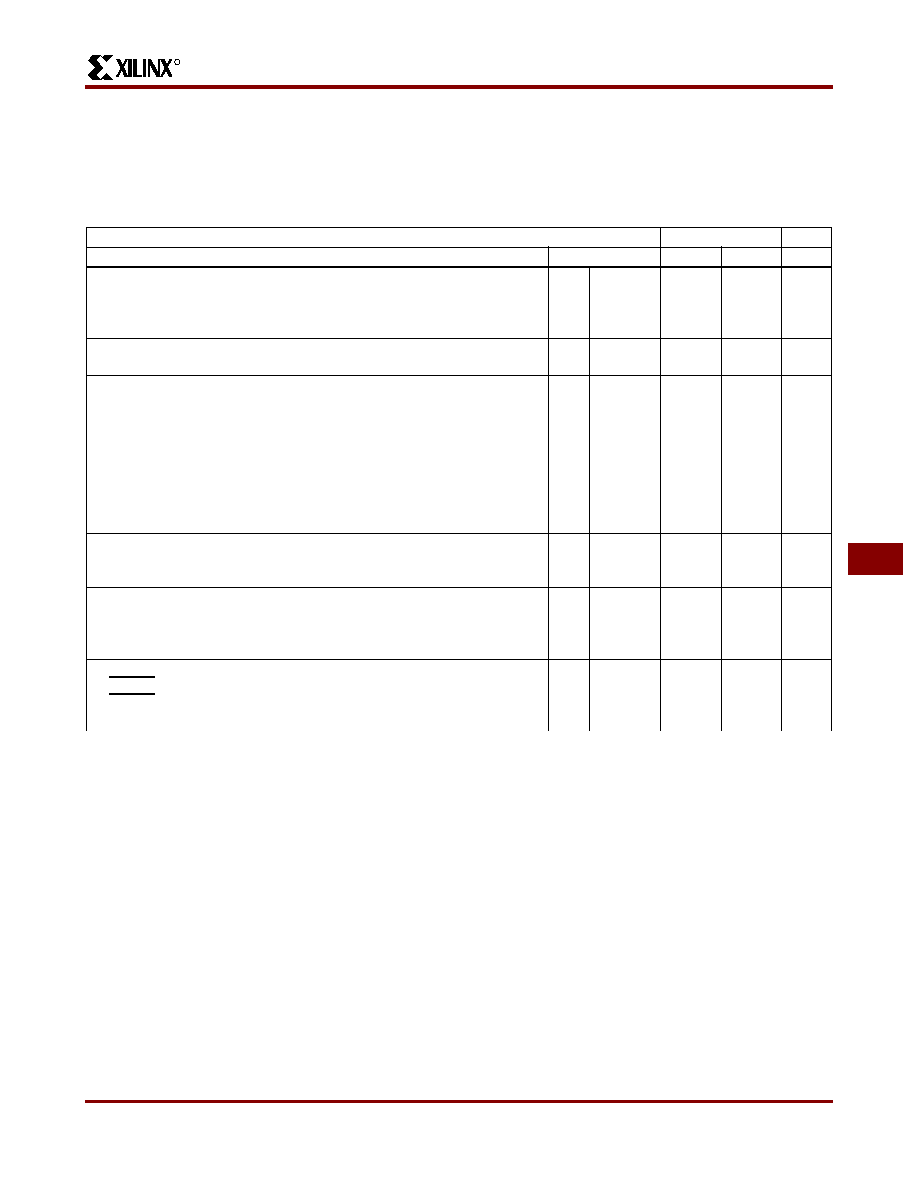

Speed Grade

-8

Description

Symbol

Min

Max

Units

Propagation Delays (Input)

Pad to Direct In (I)

Pad to Registered In (Q) with latch transparent

Clock (IK) to Registered In (Q)

3

4

TPID

TPTG

TIKRI

5.0

24.0

6.0

ns

Set-up Time (Input)

Pad to Clock (IK) set-up time

1

TPICK

22.0

ns

Propagation Delays (Output)

Clock (OK) to Pad

(fast)

same

(slew rate limited)

Output (O) to Pad

(fast)

same

(slew-rate limited)

3-state to Pad begin hi-Z

(fast)

same

(slew-rate limited)

3-state to Pad active and valid

(fast)

same

(slew -rate limited)

7

10

9

8

TOKPO

TOPF

TOPS

TTSHZ

TTSON

12.0

28.0

9.0

25.0

12.0

28.0

16.0

32.0

ns

Set-up and Hold Times (Output)

Output (O) to clock (OK) set-up time

Output (O) to clock (OK) hold time

5

6

TOOK

TOKO

12.0

0

ns

Clock

Clock High time

Clock Low time

Max. flip-flop toggle rate

11

12

TIOH

TIOL

FCLK

5.0

80.0

ns

MHz

Global Reset Delays (based on XC3042L)

RESET Pad to Registered In

(Q)

RESET Pad to output pad

(fast)

(slew-rate limited)

13

15

TRRI

TRPO

25.0

35.0

51.0

ns

Product Obsolete or Under Obsolescence

相关PDF资料 |

PDF描述 |

|---|---|

| ASM43DTMS-S189 | CONN EDGECARD 86POS R/A .156 SLD |

| XC3030A-7PC84C | IC LOGIC CL ARRAY 3000GAT 84PLCC |

| AGM43DTMS-S189 | CONN EDGECARD 86POS R/A .156 SLD |

| AYM43DTBS-S189 | CONN EDGECARD 86POS R/A .156 SLD |

| ASM43DTBS-S189 | CONN EDGECARD 86POS R/A .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC3020A-7PC84C0100 | 制造商:Xilinx 功能描述: |

| XC3020A-7PC84I | 制造商:Xilinx 功能描述: |

| XC3020A-7PCG68C | 制造商:Xilinx 功能描述: |

| XC3020A-7PQ100C | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3020A-7PQ100I | 制造商:Xilinx 功能描述: |

发布紧急采购,3分钟左右您将得到回复。