参数资料

| 型号: | XC3042A-7PQ100C |

| 厂商: | Xilinx Inc |

| 文件页数: | 19/76页 |

| 文件大小: | 0K |

| 描述: | IC LOGIC CL ARRAY 4200GAT 100PQF |

| 产品变化通告: | Product Discontinuation 27/Apr/2010 |

| 标准包装: | 1 |

| 系列: | XC3000A/L |

| LAB/CLB数: | 144 |

| RAM 位总计: | 30784 |

| 输入/输出数: | 82 |

| 门数: | 3000 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 100-BQFP |

| 供应商设备封装: | 100-QFP(14x20) |

| 其它名称: | 122-1026 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

R

XC3000 Series Field Programmable Gate Arrays

7-28

November 9, 1998 (Version 3.1)

Notes:

1. At power-up, VCC must rise from 2.0 V to VCC min in less than 25 ms. If this is not possible, configuration can be delayed by

holding RESET Low until VCC has reached 4.0 V (2.5 V for the XC3000L). A very long VCC rise time of >100 ms, or a

non-monotonically rising VCC may require a >6-s High level on RESET, followed by a >6-s Low level on RESET and D/P

after VCC has reached 4.0 V (2.5 V for the XC3000L).

2. Configuration can be controlled by holding RESET Low with or until after the INIT of all daisy-chain slave-mode devices is

High.

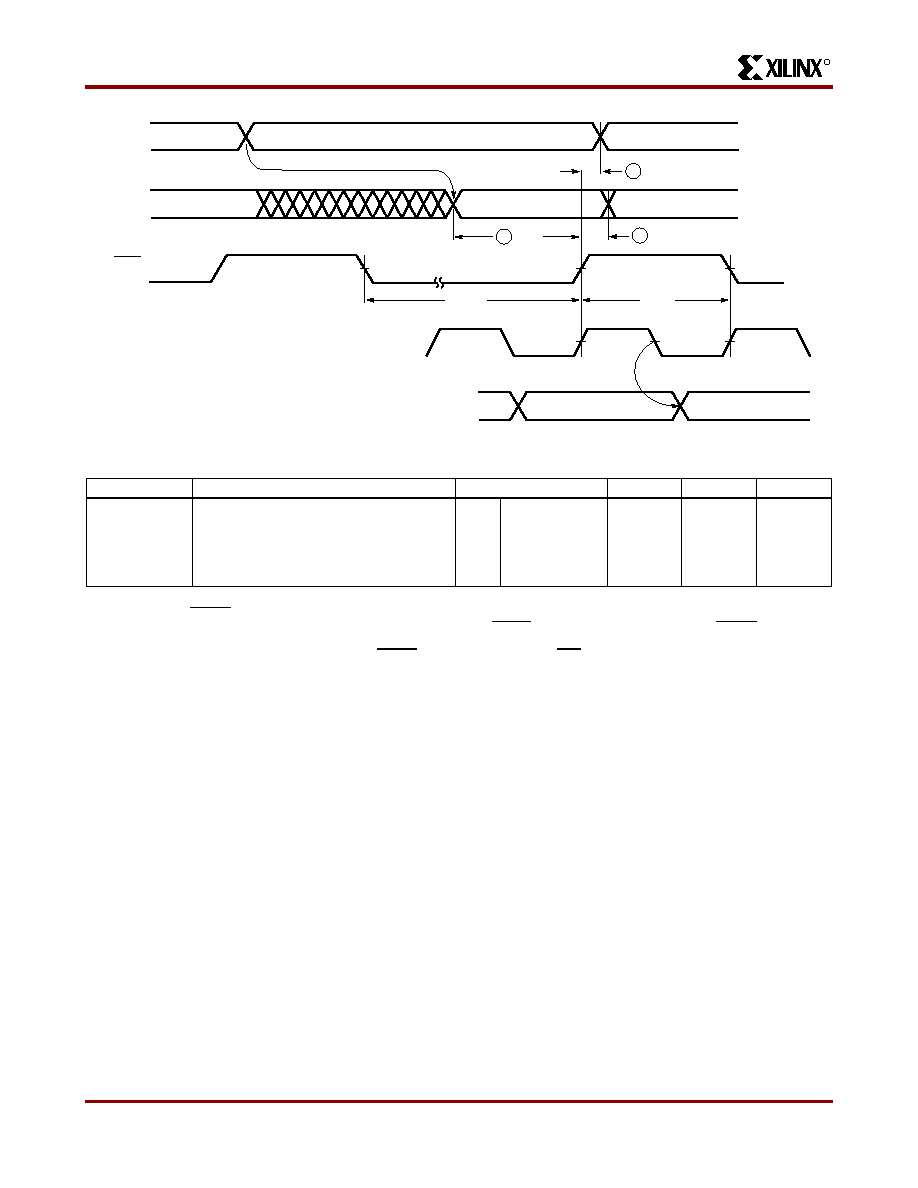

This timing diagram shows that the EPROM requirements are extremely relaxed:

EPROM access time can be longer than 4000 ns. EPROM data output has no hold time requirements.

Figure 26: Master Parallel Mode Programming Switching Characteristics

Address for Byte n

Byte

2 TDRC

Address for Byte n + 1

D7

D6

A0-A15

(output)

D0-D7

RCLK

(output)

CCLK

(output)

DOUT

(output)

1 TRAC

7 CCLKs

CCLK

3 TRCD

Byte n - 1

X5380

Description

Symbol

Min

Max

Units

RCLK

To address valid

To data setup

To data hold

RCLK High

RCLK Low

1

2

3

TRAC

TDRC

TRCD

TRCH

TRCL

0

60

0

600

4.0

200

ns

s

Product Obsolete or Under Obsolescence

相关PDF资料 |

PDF描述 |

|---|---|

| ABC65DRES-S734 | CONN EDGECARD 130PS .100 EYELET |

| A14V40A-PQG160C | IC FPGA 4K GATES 3.3V 160-PQFP |

| EMC18DTEF | CONN EDGECARD 36POS .100 EYELET |

| A1425A-1PQ160I | IC FPGA 2500 GATES 160-PQFP |

| A1440A-PQG160I | IC FPGA 4K GATES 160-PQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC3042A-7PQ100C0167 | 制造商:Xilinx 功能描述: |

| XC3042A-7PQ100C0262 | 制造商:Xilinx 功能描述: |

| XC3042A-7PQ100C0341 | 制造商:Xilinx 功能描述: |

| XC3042A-7PQ100I | 制造商: 功能描述: 制造商:undefined 功能描述: |

| XC3042A-7PQG100I | 制造商:Xilinx 功能描述: |

发布紧急采购,3分钟左右您将得到回复。