参数资料

| 型号: | XC3042A-7PQ100C |

| 厂商: | Xilinx Inc |

| 文件页数: | 47/76页 |

| 文件大小: | 0K |

| 描述: | IC LOGIC CL ARRAY 4200GAT 100PQF |

| 产品变化通告: | Product Discontinuation 27/Apr/2010 |

| 标准包装: | 1 |

| 系列: | XC3000A/L |

| LAB/CLB数: | 144 |

| RAM 位总计: | 30784 |

| 输入/输出数: | 82 |

| 门数: | 3000 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 100-BQFP |

| 供应商设备封装: | 100-QFP(14x20) |

| 其它名称: | 122-1026 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页当前第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

R

November 9, 1998 (Version 3.1)

7-53

XC3000 Series Field Programmable Gate Arrays

7

XC3100A Switching Characteristics

Xilinx maintains test specifications for each product as controlled documents. To insure the use of the most recently released

device performance parameters, please request a copy of the current test-specification revision.

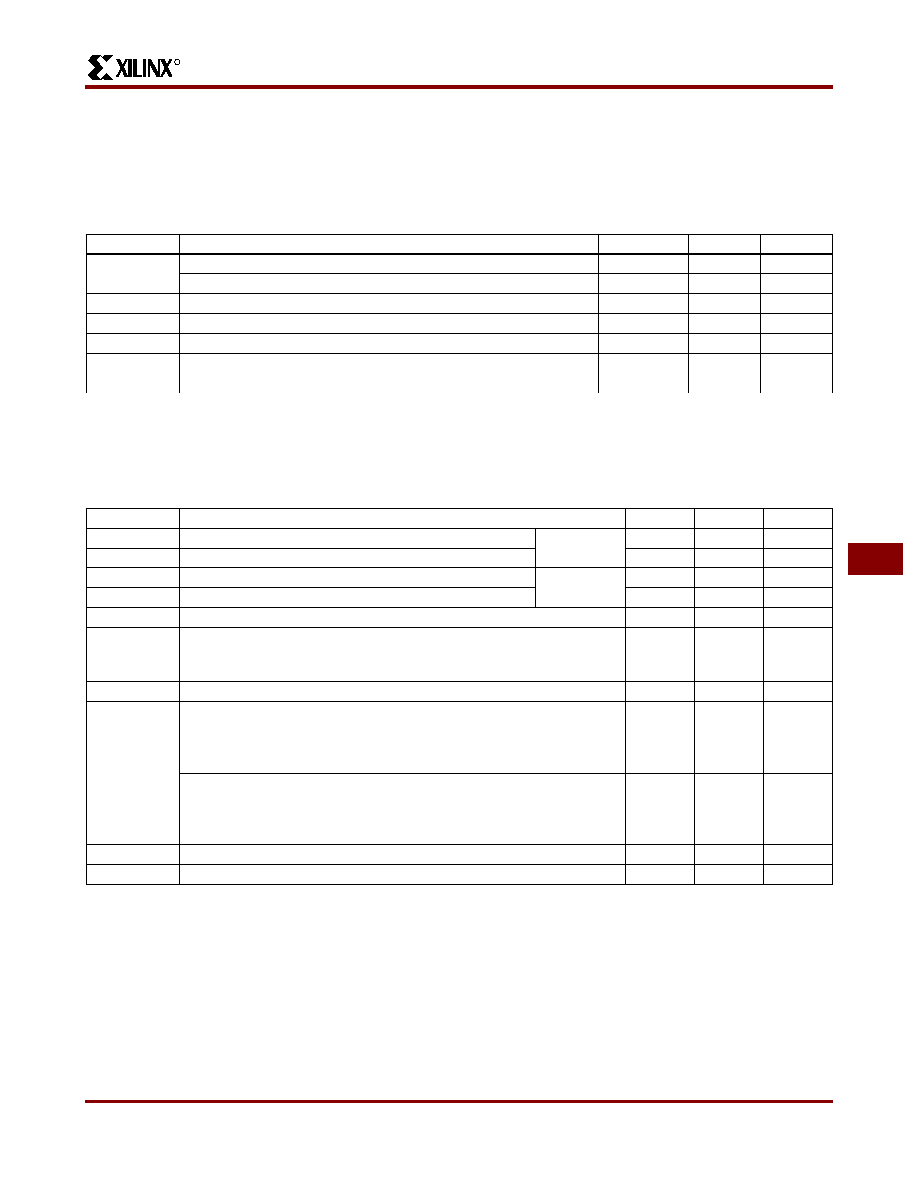

XC3100A Operating Conditions

Note:

At junction temperatures above those listed as Operating Conditions, all delay parameters increase by 0.3% per

°C.

XC3100A DC Characteristics Over Operating Conditions

Notes: 1. With no output current loads, no active input or Longline pull-up resistors, all package pins at VCC or GND, and the LCA

device configured with a tie option.

2. Total continuous output sink current may not exceed 100 mA per ground pin. The number of ground pins varies from two for

the XC3120A in the PC84 package, to eight for the XC3195A in the PQ208 package.

3. Not tested. Allows an undriven pin to float High. For any other purpose, use an external pull-up.

Symbol

Description

Min

Max

Units

VCC

Supply voltage relative to GND Commercial 0

°C to +85°C junction

4.25

5.25

V

Supply voltage relative to GND Industrial -40

°C to +100°C junction

4.5

5.5

V

VIHT

High-level input voltage — TTL configuration

2.0

VCC

V

VILT

Low-level input voltage — TTL configuration

0

0.8

V

VIHC

High-level input voltage — CMOS configuration

70%

100%

VCC

VILC

Low-level input voltage — CMOS configuration

0

20%

VCC

TIN

Input signal transition time

250

ns

Symbol

Description

Min

Max

Units

VOH

High-level output voltage (@ IOH = –8.0 mA, VCC min)

Commercial

3.86

V

VOL

Low-level output voltage (@ IOL = 8.0 mA, VCC min)

0.40

V

VOH

High-level output voltage (@ IOH = –8.0 mA, VCC min)

Industrial

3.76

V

VOL

Low-level output voltage (@ IOL = 8.0 mA, VCC min)

0.40

V

VCCPD

Power-down supply voltage (PWRDWN must be Low)

2.30

V

ICCO

Quiescent LCA supply current in addition to ICCPD

1

Chip thresholds programmed as CMOS levels

Chip thresholds programmed as TTL levels

8

14

mA

IIL

Input Leakage Current

–10

+10

A

CIN

Input capacitance, all packages except PGA175

(sample tested)

All Pins except XTL1 and XTL2

XTL1 and XTL2

10

15

pF

Input capacitance, PGA 175

(sample tested)

All Pins except XTL1 and XTL2

XTL1 and XTL2

15

20

pF

IRIN

Pad pull-up (when selected) @ VIN = 0 V

3

0.02

0.17

mA

IRLL

Horizontal Longline pull-up (when selected) @ logic Low

0.20

2.80

mA

Product Obsolete or Under Obsolescence

相关PDF资料 |

PDF描述 |

|---|---|

| ABC65DRES-S734 | CONN EDGECARD 130PS .100 EYELET |

| A14V40A-PQG160C | IC FPGA 4K GATES 3.3V 160-PQFP |

| EMC18DTEF | CONN EDGECARD 36POS .100 EYELET |

| A1425A-1PQ160I | IC FPGA 2500 GATES 160-PQFP |

| A1440A-PQG160I | IC FPGA 4K GATES 160-PQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC3042A-7PQ100C0167 | 制造商:Xilinx 功能描述: |

| XC3042A-7PQ100C0262 | 制造商:Xilinx 功能描述: |

| XC3042A-7PQ100C0341 | 制造商:Xilinx 功能描述: |

| XC3042A-7PQ100I | 制造商: 功能描述: 制造商:undefined 功能描述: |

| XC3042A-7PQG100I | 制造商:Xilinx 功能描述: |

发布紧急采购,3分钟左右您将得到回复。