- 您现在的位置:买卖IC网 > PDF目录205935 > XC5206-3BG225C (Xilinx, Inc.) Field Programmable Gate Arrays PDF资料下载

参数资料

| 型号: | XC5206-3BG225C |

| 厂商: | Xilinx, Inc. |

| 英文描述: | Field Programmable Gate Arrays |

| 中文描述: | 现场可编程门阵列 |

| 文件页数: | 35/73页 |

| 文件大小: | 598K |

| 代理商: | XC5206-3BG225C |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页当前第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页

R

XC5200 Series Field Programmable Gate Arrays

7-122

November 5, 1998 (Version 5.2)

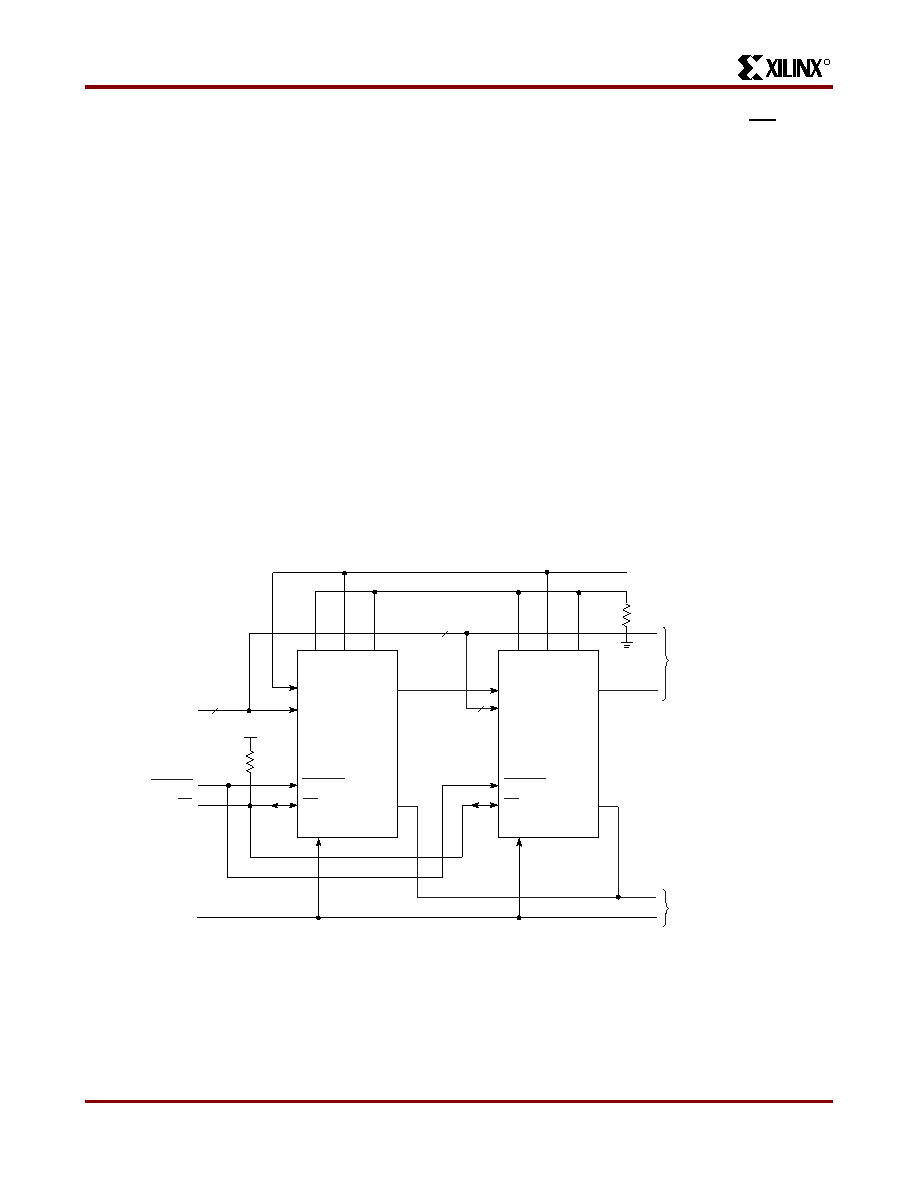

Express Mode

Express mode is similar to Slave Serial mode, except that

data is processed one byte per CCLK cycle instead of one

bit per CCLK cycle. An external source is used to drive

CCLK, while byte-wide data is loaded directly into the con-

figuration data shift registers.

A CCLK frequency of 10

MHz is equivalent to an 80 MHz serial rate, because eight

bits of configuration data are loaded per CCLK cycle.

Express mode does not support CRC error checking, but

does support constant-field error checking.

In Express mode, an external signal drives the CCLK input

of the FPGA device. The first byte of parallel configuration

data must be available at the D inputs of the FPGA a short

setup time before the second rising CCLK edge. Subse-

quent data bytes are clocked in on each consecutive rising

CCLK edge.

If the first device is configured in Express mode, additional

devices may be daisy-chained only if every device in the

chain is also configured in Express mode. CCLK pins are

tied together and D0-D7 pins are tied together for all

devices along the chain. A status signal is passed from

DOUT to CS1 of successive devices along the chain. The

lead device in the chain has its CS1 input tied High (or float-

ing, since there is an internal pullup).

Frame data is

accepted only when CS1 is High and the device’s configu-

ration memory is not already full. The status pin DOUT is

pulled Low two internal-oscillator cycles after INIT is recog-

nized as High, and remains Low until the device’s configu-

ration memory is full. DOUT is then pulled High to signal

the next device in the chain to accept the configuration data

on the D0-D7 bus.

The DONE pins of all devices in the chain should be tied

together, with one or more active internal pull-ups.

If a

large number of devices are included in the chain, deacti-

vate some of the internal pull-ups, since the Low-driving

DONE pin of the last device in the chain must sink the cur-

rent from all pull-ups in the chain. The DONE pull-up is

activated by default. It can be deactivated using an option

in the bitstream generation software.

XC5200 devices in Express mode are always synchronized

to DONE. The device becomes active after DONE goes

High. DONE is an open-drain output. With the DONE pins

tied together, therefore, the external DONE signal stays low

until all devices are configured, then all devices in the daisy

chain become active simultaneously. If the DONE pin of a

device is left unconnected, the device becomes active as

soon as that device has been configured.

Express mode is selected by a <010> on the mode pins

(M2, M1, M0).

INIT

CCLK

XC5200

M0

M1

M2

CS1

D0-D7

DATA BUS

PROGRAM

INIT

CCLK

PROGRAM

INIT

DOUT

DONE

DOUT

To Additional

Optional

Daisy-Chained

Devices

To Additional

Optional

Daisy-Chained

Devices

NOTE:

M2, M1, M0 can be shorted

to Ground if not used as I/O

Optional

Daisy-Chained

XC5200

M0

M1

VCC

4.7K

3.3 k

M2

CS1

D0-D7

PROGRAM

X6611_01

8

Figure 37: Express Mode Circuit Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| XC5206-3BG352C | Field Programmable Gate Arrays |

| XC5206-3HQ208C | Field Programmable Gate Arrays |

| XC5206-3HQ240C | Field Programmable Gate Arrays |

| XC5206-3PG156C | Field Programmable Gate Arrays |

| XC5206-3PG223C | Field Programmable Gate Arrays |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC5206-3BG352C | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5206-3HQ208C | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5206-3HQ240C | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5206-3PC84C | 制造商:Xilinx 功能描述: |

| XC5206-3PC84I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

发布紧急采购,3分钟左右您将得到回复。