- 您现在的位置:买卖IC网 > PDF目录205935 > XC5206-3BG225C (Xilinx, Inc.) Field Programmable Gate Arrays PDF资料下载

参数资料

| 型号: | XC5206-3BG225C |

| 厂商: | Xilinx, Inc. |

| 英文描述: | Field Programmable Gate Arrays |

| 中文描述: | 现场可编程门阵列 |

| 文件页数: | 37/73页 |

| 文件大小: | 598K |

| 代理商: | XC5206-3BG225C |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页

R

XC5200 Series Field Programmable Gate Arrays

7-124

November 5, 1998 (Version 5.2)

Notes: 1. A shaded table cell represents a 20-k

to 100-k pull-up resistor before and during configuration.

2. (I) represents an input (O) represents an output.

3. INIT is an open-drain output during configuration.

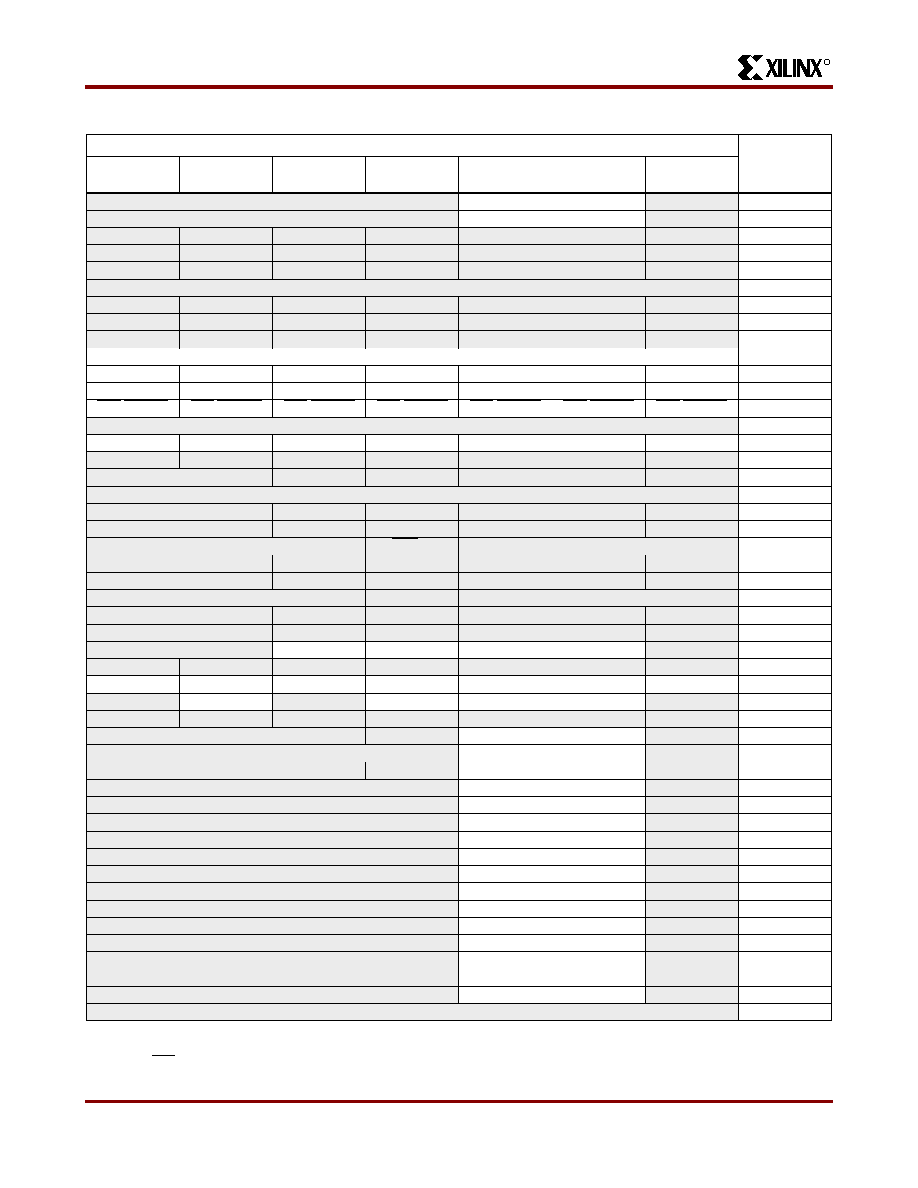

Table 13.

Pin Functions During Configuration

CONFIGURATION MODE:

<M2:M1:M0>

USER

OPERATION

SLAVE

<1:1:1>

MASTER-SER

<0:0:0>

SYN.PERIPH

<0:1:1>

ASYN.PERIPH

<1:0:1>

MASTER-HIGH

<1:1:0>

MASTER-LOW

<1:0:0>

EXPRESS

<0:1:0>

A16

GCK1-I/O

A17

I/O

TDI

TDI-I/O

TCK

TCK-I/O

TMS

TMS-I/O

I/O

M1 (HIGH) (I)

M1 (LOW) (I)

M1 (HIGH) (I)

M1 (LOW) (I)

M1 (HIGH) (I)

M1 (LOW) (I)

M1 (HIGH) (I)

I/O

M0 (HIGH) (I)

M0 (LOW) (I)

M0 (HIGH) (I)

M0 (LOW) (I)

I/O

M2 (HIGH) (I)

M2 (LOW) (I)

M2 (HIGH) (I)

M2 (LOW) (I)

I/O

GCK2-I/O

HDC (HIGH)

I/O

LDC (LOW)LDC (LOW)LDC (LOW)LDC (LOW)LDC (LOW)LDC (LOW)LDC (LOW)

I/O

INIT-ERROR

I/O

DONE

PROGRAM (I)

PROGRAM

DATA 7 (I)

I/O

GCK3-I/O

DATA 6 (I)

I/O

DATA 5 (I)

I/O

CSO (I)

I/O

DATA 4 (I)

I/O

DATA 3 (I)

I/O

RS (I)

I/O

DATA 2 (I)

I/O

DATA 1 (I)

I/O

RDY/BUSY

RCLK

I/O

DIN (I)

DATA 0 (I)

I/O

DOUT

I/O

CCLK (I)

CCLK (O)

CCLK (I)

CCLK (O)

CCLK (I)

TDO

TDO-I/O

WS (I)

A0

I/O

A1

GCK4-I/O

CS1 (I)

A2

CS1 (I)

I/O

A3

I/O

A4

I/O

A5

I/O

A6

I/O

A7

I/O

A8

I/O

A9

I/O

A10

I/O

A11

I/O

A12

I/O

A13

I/O

A14

I/O

A15

I/O

ALL OTHERS

相关PDF资料 |

PDF描述 |

|---|---|

| XC5206-3BG352C | Field Programmable Gate Arrays |

| XC5206-3HQ208C | Field Programmable Gate Arrays |

| XC5206-3HQ240C | Field Programmable Gate Arrays |

| XC5206-3PG156C | Field Programmable Gate Arrays |

| XC5206-3PG223C | Field Programmable Gate Arrays |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC5206-3BG352C | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5206-3HQ208C | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5206-3HQ240C | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5206-3PC84C | 制造商:Xilinx 功能描述: |

| XC5206-3PC84I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

发布紧急采购,3分钟左右您将得到回复。