参数资料

| 型号: | XC6SLX25T-2FG484I |

| 厂商: | Xilinx Inc |

| 文件页数: | 81/89页 |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN 6 484FGGBGA |

| 标准包装: | 60 |

| 系列: | Spartan® 6 LXT |

| LAB/CLB数: | 1879 |

| 逻辑元件/单元数: | 24051 |

| RAM 位总计: | 958464 |

| 输入/输出数: | 250 |

| 电源电压: | 1.14 V ~ 1.26 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 484-BBGA |

| 供应商设备封装: | 484-FBGA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页当前第81页第82页第83页第84页第85页第86页第87页第88页第89页

Spartan-6 FPGA Data Sheet: DC and Switching Characteristics

DS162 (v3.0) October 17, 2011

Product Specification

82

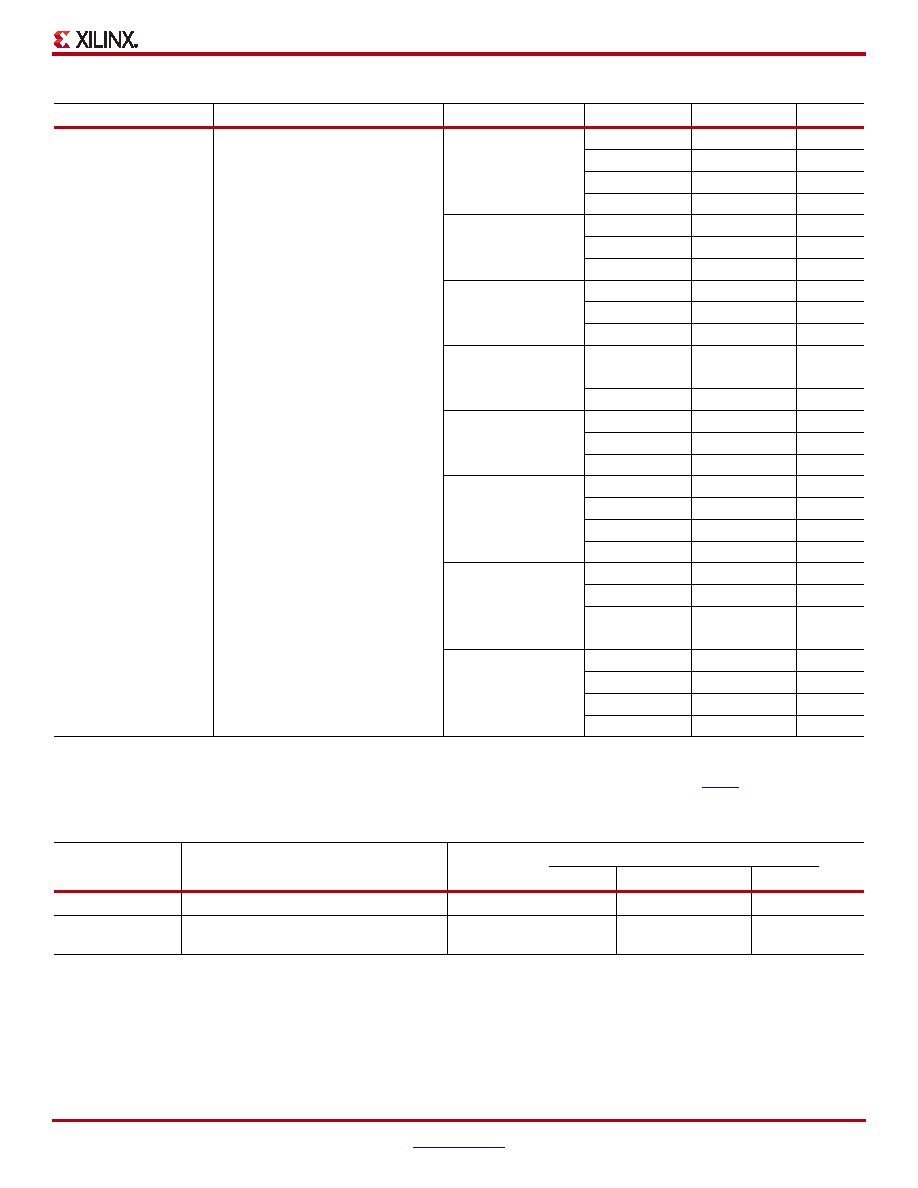

TPKGSKEW

Package Skew(1)

LX45

CSG324

70

ps

CS(G)484

99

ps

FG(G)484

109

ps

FG(G)676

138

ps

LX45T

CSG324

75

ps

CS(G)484

100

ps

FG(G)484

95

ps

LX75

CS(G)484

101

ps

FG(G)484

107

ps

FG(G)676

161

ps

LX75T

CS(G)484

107

ps

FG(G)484

110

ps

FG(G)676

134

ps

LX100

CS(G)484

95

ps

FG(G)484

155

ps

FG(G)676

144

ps

LX100T

CS(G)484

88

ps

FG(G)484

111

ps

FG(G)676

147

ps

FG(G)900

134

ps

LX150

CS(G)484

84

ps

FG(G)484

103

ps

FG(G)676

115

ps

FG(G)900

121

ps

LX150T

CS(G)484

83

ps

FG(G)484

88

ps

FG(G)676

141

ps

FG(G)900

120

ps

Notes:

1.

These values represent the worst-case skew between any two SelectIO resources in the package: shortest delay to longest delay from Pad to Ball.

2.

Some of the devices are available in both Pb and Pb-free (additional G) packages as standard ordering options. See DS160: Spartan-6 Family

Overview for more information.

Table 80: Sample Window

Symbol

Description

Device(1)

Speed Grade

Units

-3

-3N

-2

-1L

TSAMP

Sampling Error at Receiver Pins(2)

All

510

530

740

ps

TSAMP_BUFIO2

Sampling Error at Receiver Pins using

BUFIO2(3)

All

430

450

590

ps

Notes:

1.

LXT devices are not available with a -1L speed grade.

2.

This parameter indicates the total sampling error of Spartan-6 FPGA DDR input registers, measured across voltage, temperature, and process. The

characterization methodology uses the DCM to capture the DDR input registers’ edges of operation. These measurements include:

- CLK0 DCM jitter

- DCM accuracy (phase offset)

- DCM phase shift resolution

These measurements do not include package or clock tree skew.

3.

This parameter indicates the total sampling error of Spartan-6 FPGA DDR input registers, measured across voltage, temperature, and process. The

characterization methodology uses the BUFIO2 clock network and IODELAY2 to capture the DDR input registers’ edges of operation. These

measurements do not include package or clock tree skew.

Table 79: Package Skew (Cont’d)

Symbol

Description

Device

Package(2)

Value

Units

相关PDF资料 |

PDF描述 |

|---|---|

| GCB106DHBS-S621 | CONN EDGECARD 212PS R/A .050 SLD |

| ABB55DHAS | CONN EDGECARD 110PS R/A .050 SLD |

| XC6SLX25T-2FGG484I | IC FPGA SPARTAN 6 24K 484FGGBGA |

| XC2V250-4CSG144C | IC FPGA VIRTEX-II 250K 144-CSBGA |

| ASC43DRYN-S734 | CONN EDGECARD 86POS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC6SLX25T-2FGG484C | 功能描述:IC FPGA SPARTAN 6 24K 484FGGBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan® 6 LXT 标准包装:24 系列:ECP2 LAB/CLB数:1500 逻辑元件/单元数:12000 RAM 位总计:226304 输入/输出数:131 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) |

| XC6SLX25T-2FGG484I | 功能描述:IC FPGA SPARTAN 6 24K 484FGGBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan® 6 LXT 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XC6SLX25T-3CSG324C | 功能描述:IC FPGA SPARTAN 6 24K 324CSGBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan® 6 LXT 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XC6SLX25T-3CSG324I | 功能描述:IC FPGA SPARTAN 6 24K 324CSGBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan® 6 LXT 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XC6SLX25T-3FG484C | 制造商:Xilinx 功能描述:FPGA SPARTAN?-6 FAMILY 24051 CELLS 45NM (CMOS) TECHNOLOGY 1. - Trays 制造商:Xilinx 功能描述:IC FPGA SPARTAN 6 25K 484BGA 制造商:Xilinx 功能描述:IC FPGA 250 I/O 484FBGA |

发布紧急采购,3分钟左右您将得到回复。