参数资料

| 型号: | XC6VCX130T-2FFG784C |

| 厂商: | Xilinx Inc |

| 文件页数: | 25/52页 |

| 文件大小: | 0K |

| 描述: | IC FPGA VIRTEX 6 128K 784FFGBGA |

| 产品培训模块: | Virtex-6 FPGA Overview |

| 产品变化通告: | Virtex-6 FIFO Input Logic Reset 18/Apr/2011 |

| 标准包装: | 1 |

| 系列: | Virtex® 6 CXT |

| LAB/CLB数: | 10000 |

| 逻辑元件/单元数: | 128000 |

| RAM 位总计: | 9732096 |

| 输入/输出数: | 400 |

| 电源电压: | 0.95 V ~ 1.05 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 784-BBGA,FCBGA |

| 供应商设备封装: | 784-FCBGA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

Virtex-6 CXT Family Data Sheet

DS153 (v1.6) February 11, 2011

Product Specification

31

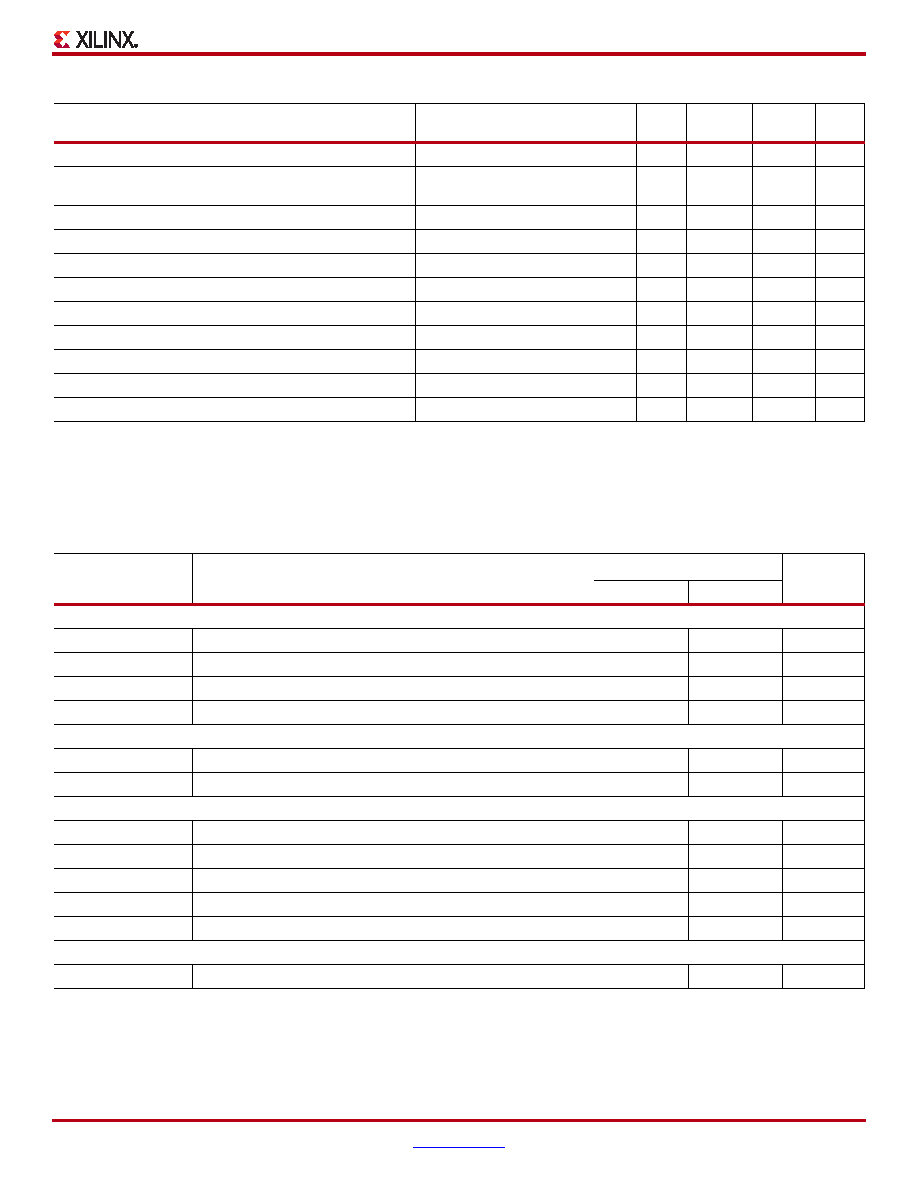

Input/Output Logic Switching Characteristics

HT (HyperTransport), 2.5V

LDT_25

100

0

0(2)

0.6

LVPECL (Low-Voltage Positive Emitter-Coupled Logic),

2.5V

LVPECL_25

100

0

0

LVDCI/HSLVDCI, 2.5V

LVDCI_25, HSLVDCI_25

1M

0

1.25

0

LVDCI/HSLVDCI, 1.8V

LVDCI_18, HSLVDCI_18

1M

0

0.9

0

LVDCI/HSLVDCI, 1.5V

LVDCI_15, HSLVDCI_15

1M

0

0.75

0

HSTL (High-Speed Transceiver Logic), Class I & II, with DCI HSTL_I_DCI, HSTL_II_DCI

50

0

VREF

0.75

HSTL, Class III, with DCI

HSTL_III_DCI

50

0

0.9

1.5

HSTL, Class I & II, 1.8V, with DCI

HSTL_I_DCI_18, HSTL_II_DCI_18

50

0

VREF

0.9

HSTL, Class III, 1.8V, with DCI

HSTL_III_DCI_18

50

0

1.1

1.8

SSTL (Stub Series Termi.Logic), Class I & II, 1.8V, with DCI SSTL18_I_DCI, SSTL18_II_DCI

50

0

VREF

0.9

SSTL, Class I & II, 2.5V, with DCI

SSTL2_I_DCI, SSTL2_II_DCI

50

0

VREF

1.25

Notes:

1.

CREF is the capacitance of the probe, nominally 0 pF.

2.

The value given is the differential output voltage.

Table 42: ILOGIC Switching Characteristics

Symbol

Description

Speed Grade

Units

-2

-1

Setup/Hold

TICE1CK/TICKCE1

CE1 pin Setup/Hold with respect to CLK

0.27/0.04

ns

TISRCK/TICKSR

SR pin Setup/Hold with respect to CLK

0.96/–0.10

ns

TIDOCK/TIOCKD

D pin Setup/Hold with respect to CLK without Delay

0.10/0.54

ns

TIDOCKD/TIOCKDD

DDLY pin Setup/Hold with respect to CLK (using IODELAY)

0.14/0.42

0.14/0.40

ns

Combinatorial

TIDI

D pin to O pin propagation delay, no Delay

0.20

ns

TIDID

DDLY pin to O pin propagation delay (using IODELAY)

0.25

ns

Sequential Delays

TIDLO

D pin to Q1 pin using flip-flop as a latch without Delay

0.64

ns

TIDLOD

DDLY pin to Q1 pin using flip-flop as a latch (using IODELAY)

0.68

ns

TICKQ

CLK to Q outputs

0.71

ns

TRQ_ILOGIC

SR pin to OQ/TQ out

1.15

ns

TGSRQ_ILOGIC

Global Set/Reset to Q outputs

10.51

ns

Set/Reset

TRPW_ILOGIC

Minimum Pulse Width, SR inputs

1.20

ns, Min

Table 41: Output Delay Measurement Methodology (Cont’d)

Description

I/O Standard

Attribute

RREF

(

)

CREF(1)

(pF)

VMEAS

(V)

VREF

(V)

相关PDF资料 |

PDF描述 |

|---|---|

| XC4VLX60-10FF668I | IC FPGA VIRTEX-4LX 668FFBGA |

| XC6VLX75T-L1FFG784C | IC FPGA VIRTEX 6 74K 784FFGBGA |

| XCV400E-8FG676C | IC FPGA 1.8V C-TEMP 676-FBGA |

| XCV400E-8BG560C | IC FPGA 1.8V C-TEMP 560-MBGA |

| BR25L010FV-WE2 | IC EEPROM SER 1KB SPI BUS 8SSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC6VCX130T-2FFG784I | 功能描述:IC FPGA VIRTEX 6 128K 784FFGBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex® 6 CXT 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC6VCX195T | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-6 CXT Family Data Sheet |

| XC6VCX195T-1FF1156C | 制造商:Xilinx 功能描述:FPGA VIRTEX?-6 CXT FAMILY 199680 CELLS 40NM (CMOS) TECHNOLOG - Trays 制造商:Xilinx 功能描述:IC FPGA VIRTEX 6 195K 1156BGA |

| XC6VCX195T-1FF1156I | 制造商:Xilinx 功能描述:FPGA VIRTEX?-6 CXT FAMILY 199680 CELLS 40NM (CMOS) TECHNOLOG - Trays 制造商:Xilinx 功能描述:IC FPGA VIRTEX 6 195K 1156BGA |

| XC6VCX195T-1FF784C | 制造商:Xilinx 功能描述:FPGA VIRTEX?-6 CXT FAMILY 199680 CELLS 40NM (CMOS) TECHNOLOG - Trays 制造商:Xilinx 功能描述:IC FPGA VIRTEX 6 195K 784BGA |

发布紧急采购,3分钟左右您将得到回复。