- 您现在的位置:买卖IC网 > PDF目录16451 > XR16V794IV-0B-EVB (Exar Corporation)EVAL BOARD FOR XR16V794-B 64TQFP PDF资料下载

参数资料

| 型号: | XR16V794IV-0B-EVB |

| 厂商: | Exar Corporation |

| 文件页数: | 35/53页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XR16V794-B 64TQFP |

| 设计资源: | XR17V798/794 Eval Board Schematic |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页当前第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页

XR16V794

40

HIGH PERFORMANCE 2.25V TO 3.6V QUAD UART WITH FRACTIONAL BAUD RATE

REV. 1.0.1

EFR[5]: Special Character Detect Enable

Logic 0 = Special Character Detect Disabled (default).

Logic 1 = Special Character Detect Enabled. The UART compares each incoming receive character with

data in Xoff-2 register. If a match exists, the received data will be transferred to FIFO and ISR bit-4 will be set

to indicate detection of the special character. Bit-0 corresponds with the LSB bit for the receive character. If

flow control is set for comparing Xon1, Xoff1 (EFR [1:0]=10) then flow control and special character work

normally. However, if flow control is set for comparing Xon2, Xoff2 (EFR[1:0]=01) then flow control works

normally, but Xoff2 will not go to the FIFO, and will generate an Xoff interrupt and a special character

interrupt.

EFR[4]: Enhanced Function Bits Enable

Enhanced function control bit. This bit enables the enhanced functions in IER bits 7:5, ISR bits 5:4, FCR bits

5:4, MCR bits 7:5, 3:2 and MSR 7:2 bits to be modified. After modifying any enhanced bits, EFR bit-4 can be

set to a logic 0 to latch the new values. This feature prevents legacy software from altering or overwriting the

enhanced functions once set. Normally, it is recommended to leave it enabled, logic 1.

Logic 0 = modification disable/latch enhanced features. IER bits 7:5, ISR bits 5:4, FCR bits 5:4, MCR bits 7:5,

3:2 and MSR 7:2 bits are saved to retain the user settings. After a reset, all these bits are set to a logic 0 to

be compatible with ST16C550 mode (default).

Logic 1 = Enables the enhanced functions. When this bit is set to a logic 1 all enhanced features are

enabled.

EFR[3:0]: Software Flow Control Select

Combinations of software flow control can be selected by programming these bits, as shown in Table 18

below.

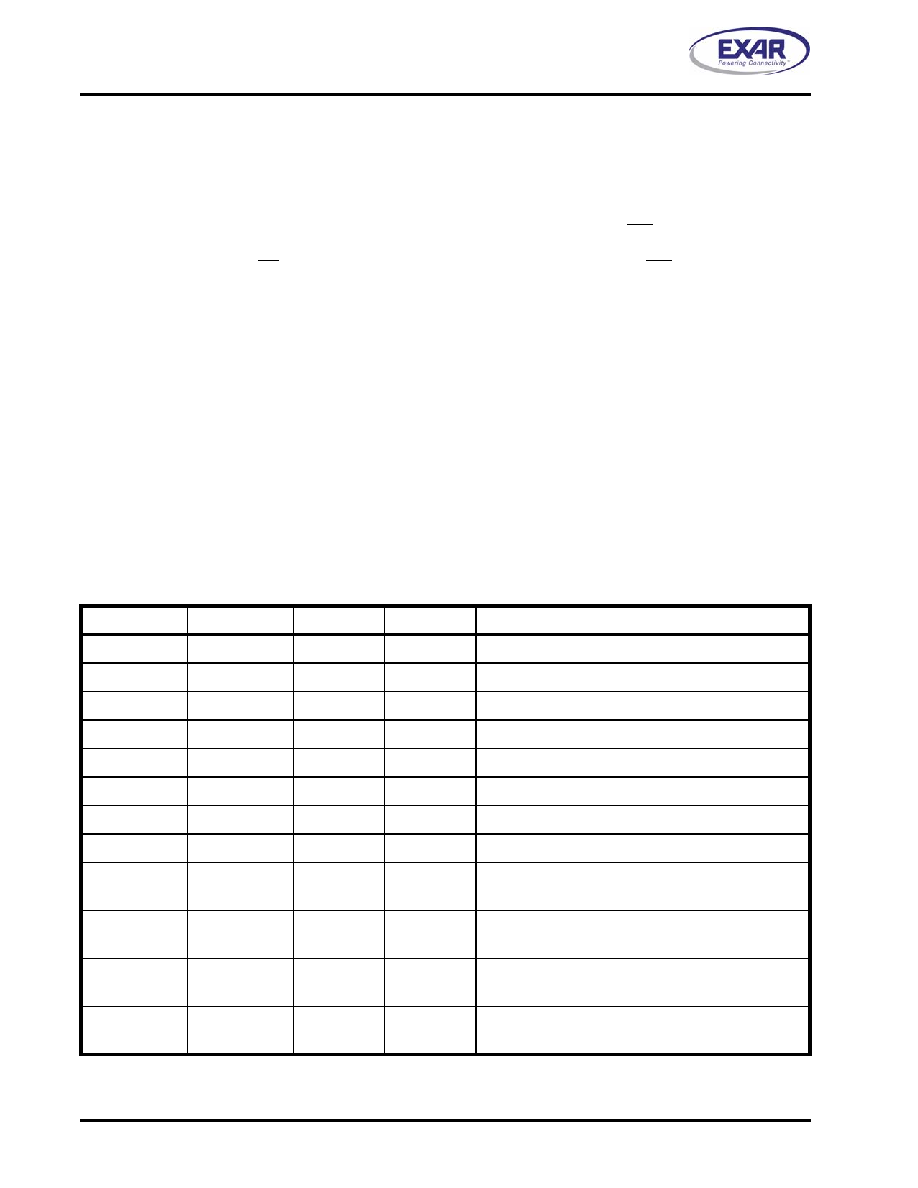

TABLE 18: SOFTWARE FLOW CONTROL FUNCTIONS

EFR BIT-3

EFR BIT-2

EFR BIT-1

EFR BIT-0

TRANSMIT AND RECEIVE SOFTWARE FLOW CONTROL

0

No TX and RX flow control (default and reset)

0

X

No transmit flow control

1

0

X

Transmit Xon1, Xoff1

0

1

X

Transmit Xon2, Xoff2

1

X

Transmit Xon1 and Xon2, Xoff1 and Xoff2

X

0

No receive flow control

X

1

0

Receiver compares Xon1, Xoff1

X

0

1

Receiver compares Xon2, Xoff2

1

0

1

Transmit Xon1, Xoff1

Receiver compares Xon1 or Xon2, Xoff1 or Xoff2

0

1

Transmit Xon2, Xoff2

Receiver compares Xon1 or Xon2, Xoff1 or Xoff2

1

Transmit Xon1 and Xon2, Xoff1 and Xoff2

Receiver compares Xon1 and Xon2, Xoff1 and Xoff2

0

1

No transmit flow control

Receiver compares Xon1 and Xon2, Xoff1 and Xoff2

相关PDF资料 |

PDF描述 |

|---|---|

| 1-1906053-1 | CA 2MM OFNR 62.5/125,LC SEC YEL |

| D-1744-02 | SOLDERSLEEVE WIRE SPLICE .125" |

| GCC10DRAH-S734 | CONN EDGECARD 20POS .100 R/A SLD |

| A3977SLP-T | IC MOTOR DRIVER PWM DUAL 28-TSSO |

| 1-1906052-1 | CA 2MM OFNR 62.5/125,LC SEC BLU |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR16V794IV-F | 功能描述:UART 接口集成电路 UART RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR16V798 | 制造商:EXAR 制造商全称:EXAR 功能描述:HIGH PERFORMANCE 2.25V TO 3.6V OCTAL UART WITH FRACTIONAL |

| XR16V798_08 | 制造商:EXAR 制造商全称:EXAR 功能描述:HIGH PERFORMANCE 2.25V TO 3.6V OCTAL UART WITH FRACTIONAL |

| XR16V798IQ | 制造商:EXAR 制造商全称:EXAR 功能描述:HIGH PERFORMANCE 2.25V TO 3.6V OCTAL UART WITH FRACTIONAL |

| XR16V798IQ-0A-EVB | 功能描述:UART 接口集成电路 Supports V798 100 ld QFP,ISA Interface RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。