- 您现在的位置:买卖IC网 > PDF目录300164 > ZL50418/GKC (ZARLINK SEMICONDUCTOR INC) DATACOM, LAN SWITCHING CIRCUIT, PBGA553 PDF资料下载

参数资料

| 型号: | ZL50418/GKC |

| 厂商: | ZARLINK SEMICONDUCTOR INC |

| 元件分类: | 网络接口 |

| 英文描述: | DATACOM, LAN SWITCHING CIRCUIT, PBGA553 |

| 封装: | 37.50 X 37.50 MM, 2.33 MM HEIGHT, MS-034, HSBGA-553 |

| 文件页数: | 99/155页 |

| 文件大小: | 1928K |

| 代理商: | ZL50418/GKC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页当前第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页

ZL50418

Data Sheet

48

Zarlink Semiconductor Inc.

During scheduling, the TxQ manager treats the unicast queue and the multicast queue of the same class as one

logical queue. The older head of line of the two queues is forwarded first.

The port control requests a FCB release only after the EOF for the multicast frame has been read by all ports to

which the frame is destined.

4.3

Frame Forwarding To and From CPU

Frame forwarding from the CPU port to a regular transmission port is nearly the same as forwarding between

transmission ports. The only difference is that the physical destination port must be indicated in addition to the

destination MAC address.

Frame forwarding to the CPU port is nearly the same as forwarding to a regular transmission port. The only

difference is in frame scheduling. Instead of using the patent-pending Zarlink Semiconductor scheduling algorithms,

scheduling for the CPU port is simply based on strict priority. That is, a frame in a high priority queue will always be

transmitted before a frame in a lower priority queue. There are four output queues to the CPU and one receive

queue.

5.0

Memory Interface

5.1

Overview

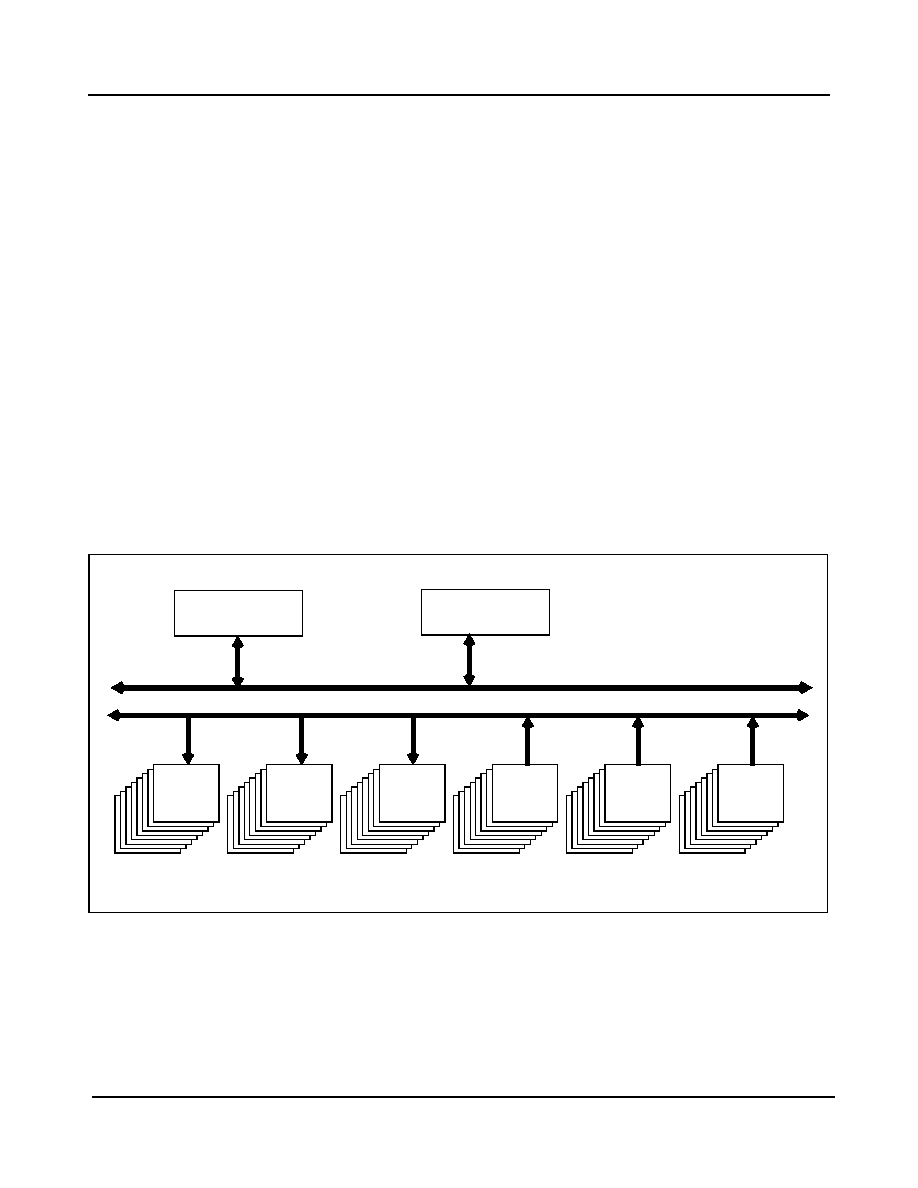

The ZL50418 provides two 64-bit wide SRAM banks, SRAM Bank A and SRAM Bank B. Each DMA can read and

write from both bank A and bank B. The following figure provides an overview of the ZL50418 SRAM banks.

Figure 8 - SRAM Interface Block Diagram (DMAs for 10/100 Ports Only)

Because the bus for each bank is 64 bits wide, frames are broken into 8-byte granules, written to and read from

memory. The first 8-byte granule gets written to Bank A, the second 8-byte granule gets written to Bank B and so on

in alternating fashion. When reading frames from memory, the same procedure is followed, first from A, then from B

and so on.

The reading and writing from alternating memory banks can be performed with minimal waste of memory

bandwidth. What’s the worst case? For any speed port, in the worst case, a 1-byte-long EOF granule gets written to

SRAM

TX DMA

0-7

TX DMA

8-15

TX DMA

16-23

RX DMA

0-7

RX DMA

8-15

RX DMA

16-23

SRAM

相关PDF资料 |

PDF描述 |

|---|---|

| ZL50418GKG2 | DATACOM, LAN SWITCHING CIRCUIT, PBGA553 |

| ZLW-2-B | 1 MHz - 1000 MHz RF/MICROWAVE DOUBLE BALANCED MIXER, 9.5 dB CONVERSION LOSS-MAX |

| ZMG71W | SINGLE COLOR LED, GREEN |

| ZMM5228/D1 | 3.9 V, 0.5 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

| ZMM5242/D1 | 12 V, 0.5 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ZL51B | 制造商:YEASHIN 制造商全称:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL56B | 制造商:YEASHIN 制造商全称:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL5V1B | 制造商:YEASHIN 制造商全称:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL5V6B | 制造商:YEASHIN 制造商全称:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL60001 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:High speed 2.5 Gbps 850 nm VCSEL |

发布紧急采购,3分钟左右您将得到回复。