- 您现在的位置:买卖IC网 > PDF目录300164 > ZL50418GKG2 (ZARLINK SEMICONDUCTOR INC) DATACOM, LAN SWITCHING CIRCUIT, PBGA553 PDF资料下载

参数资料

| 型号: | ZL50418GKG2 |

| 厂商: | ZARLINK SEMICONDUCTOR INC |

| 元件分类: | 网络接口 |

| 英文描述: | DATACOM, LAN SWITCHING CIRCUIT, PBGA553 |

| 封装: | 37.50 X 37.50 MM, 2.33 MM HEIGHT, LEAD FREE, MS-034, HSBGA-553 |

| 文件页数: | 87/155页 |

| 文件大小: | 1928K |

| 代理商: | ZL50418GKG2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页当前第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页

ZL50418

Data Sheet

37

Zarlink Semiconductor Inc.

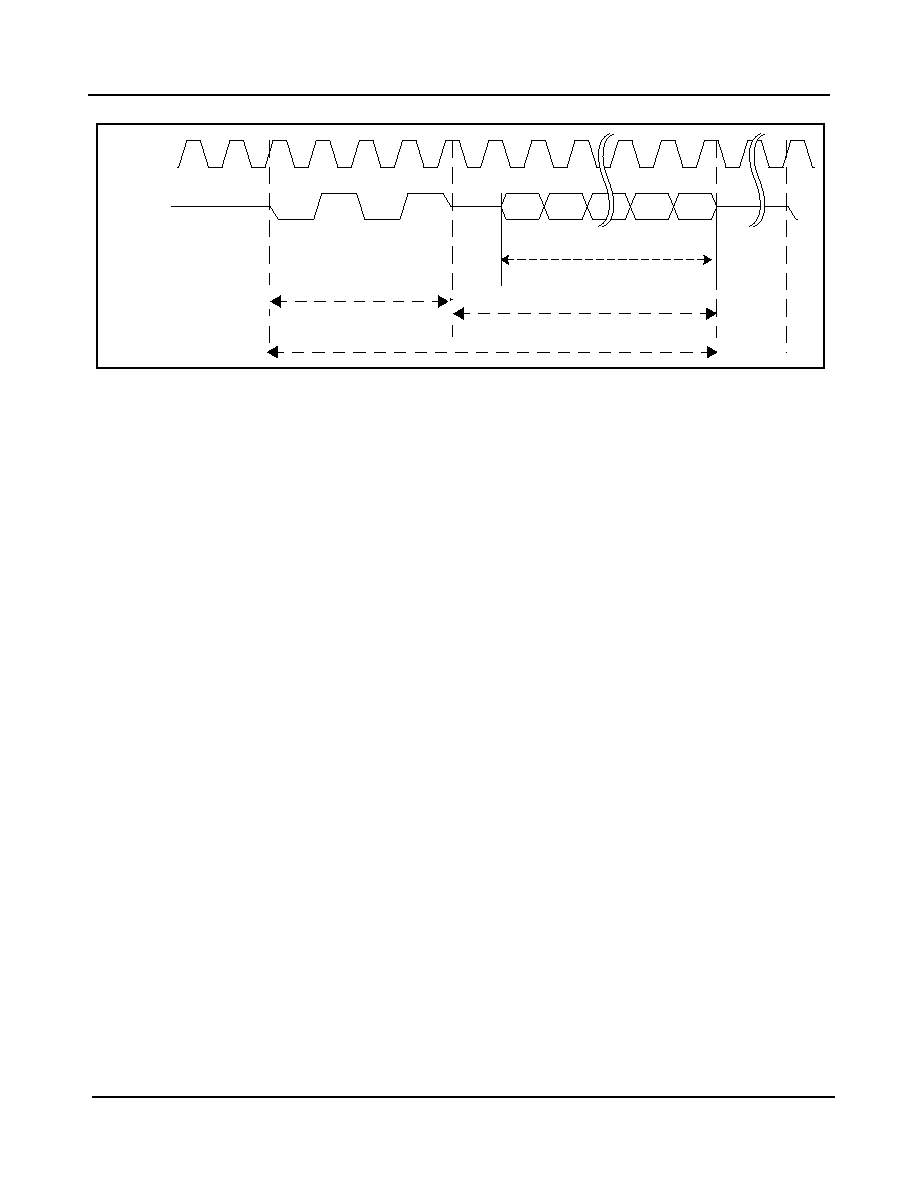

Figure 3 - SCANLINK and SCANCOL Status Diagram

2.2.2

GMII MAC Module (GMAC)

The 10/100/1000 M Media Access Control (MAC) module provides the necessary buffers and control interface

between the Frame Engine (FE) and the external physical device (PHY). The ZL50418 GMAC implements both

GMII and MII interface, which offers a simple migration from 10/100 M to 1000 M.

The GMAC of the ZL50418 meets the IEEE 802.3Z specification. It is able to operate in 10/100M either Half or Full

Duplex mode with a back pressure/flow control mechanism or in 1G Full duplex mode with flow control mechanism.

Furthermore, it will automatically retransmit upon collision for up to 16 total transmissions.

The PHY addresses for the two GMACs are 01h and 02h. These two ports are denoted as ports 25 (G0) and 26

(G1).

For fiber optics media, the ZL50418 implements the Physical Code Sublayer (PCS) interface. The PCS includes an

8B10B encoder and decoder, auto-negotiation and Ten Bit Interface (TBI)

2.2.2.1

Physical Coding Sublayer (PCS) Module

For the ZL50418, the 1000BASE-X PCS module is designed internally and may be utilized in the absence of GMII.

The PCS incorporates all the functions required by the GMII to include encoding (decoding) 8B GMII data to (from)

8B/10B TBI format for PHY communication and generating Collision Detect (COL) signals for half-duplex mode. It

also manages the auto-negotiation process by informing the management entity that the PHY is ready for

communications. The on-chip PCS may be disabled if a PCS block exists within the Gigabit PHY. The TBI interface

provides a uniform interface for all 1000 Mbps PHY implementations.

The PCS comprises the PCS Transmit, Synchronization, PCS Receive and auto-negotiation processes for

1000BASE-X.

The PCS Transmit process sends the TBI signals TXD[9:0] to the physical medium and generates the GMII

Collision Detect (COL) signal based on whether a reception is occurring simultaneously with transmission.

Additionally, the Transmit process generates an internal “transmitting” flag and monitors auto-negotiation to

determine whether to transmit data or to reconfigure the link.

The PCS Synchronization process determines whether or not the receive channel is operational.

The PCS Receive process receives the TBI signals RXD[9:0] from the physical medium, and generates the GMII

RXD[7:0] signals and the internal “receiving” flag for use by the Transmit processes.

scan_clk

scan_link/

scan_col

Drived by VTX260x

Drived by CPLD

25 cycles for link/

24 cycles for col

Total 32 cycles period

Drived by device

Drived by CPLD

Total 32 cycles period

相关PDF资料 |

PDF描述 |

|---|---|

| ZLW-2-B | 1 MHz - 1000 MHz RF/MICROWAVE DOUBLE BALANCED MIXER, 9.5 dB CONVERSION LOSS-MAX |

| ZMG71W | SINGLE COLOR LED, GREEN |

| ZMM5228/D1 | 3.9 V, 0.5 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

| ZMM5242/D1 | 12 V, 0.5 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

| ZMV934ATC | VHF BAND, 12 V, SILICON, HYPERABRUPT VARIABLE CAPACITANCE DIODE |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ZL51B | 制造商:YEASHIN 制造商全称:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL56B | 制造商:YEASHIN 制造商全称:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL5V1B | 制造商:YEASHIN 制造商全称:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL5V6B | 制造商:YEASHIN 制造商全称:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL60001 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:High speed 2.5 Gbps 850 nm VCSEL |

发布紧急采购,3分钟左右您将得到回复。