- 您现在的位置:买卖IC网 > PDF目录67311 > 4450HG/3-K (EXAR CORP) MICROPROCESSOR, PBGA324 PDF资料下载

参数资料

| 型号: | 4450HG/3-K |

| 厂商: | EXAR CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | MICROPROCESSOR, PBGA324 |

| 封装: | ROHS COMPLIANT, HSBGA-324 |

| 文件页数: | 24/92页 |

| 文件大小: | 780K |

| 代理商: | 4450HG/3-K |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

4450 – Data Sheet, DS-0131-06

Page 30

Hifn Confidential

There are two pins that are sampled coming out of Reset and control the boot process,

dpu_gpio[1]/boot_config_1 and dpu_gpio[0]/boot_config_0. These two pins are

further defined in Section 6.7. Table 5-1 summarizes how these two pins are used to

control the boot process.

If the boot_config_1 pin is tied high it indicates that the 4450 has a Flash device

connected. In order to boot from a Flash device, a minimal amount of SDRAM must be

connected to the 4450. If boot_config_1 is tied low it indicates that there is no Flash

device connected to 4450, and the pre-boot code attempts to download boot code from

one of the host Ethernet ports.

The boot_config_0 pin indicates if downloading boot code from one of the host GMAC

ports is permitted. This can be useful for FIPS 140-2 subsystem certification. If the

boot_config_1 pin is pulled low, then booting from one of the host GMAC ports is allowed.

If boot_config_0 pin is pulled high, then booting from the host 0 or host 1 GMAC port is

not allowed.

The eSC processor first looks at the boot_config_1 pin to see if a Flash is present. Then

the DPU will look at boot_config_0 to see if listening to the host GMAC ports is allowed.

If there is no Flash device (boot_config_1 = 0) or the Flash boot fails, and listening to

the host port times out (eSC listening to RMII port and DPU listening to host ports), then

the eSC and DPU will each listen to each other for booting across the inter-connect bus

used for inter-processor communication.

For full details on the software boot load process, refer to the 44x0/84x0 User's Manual.

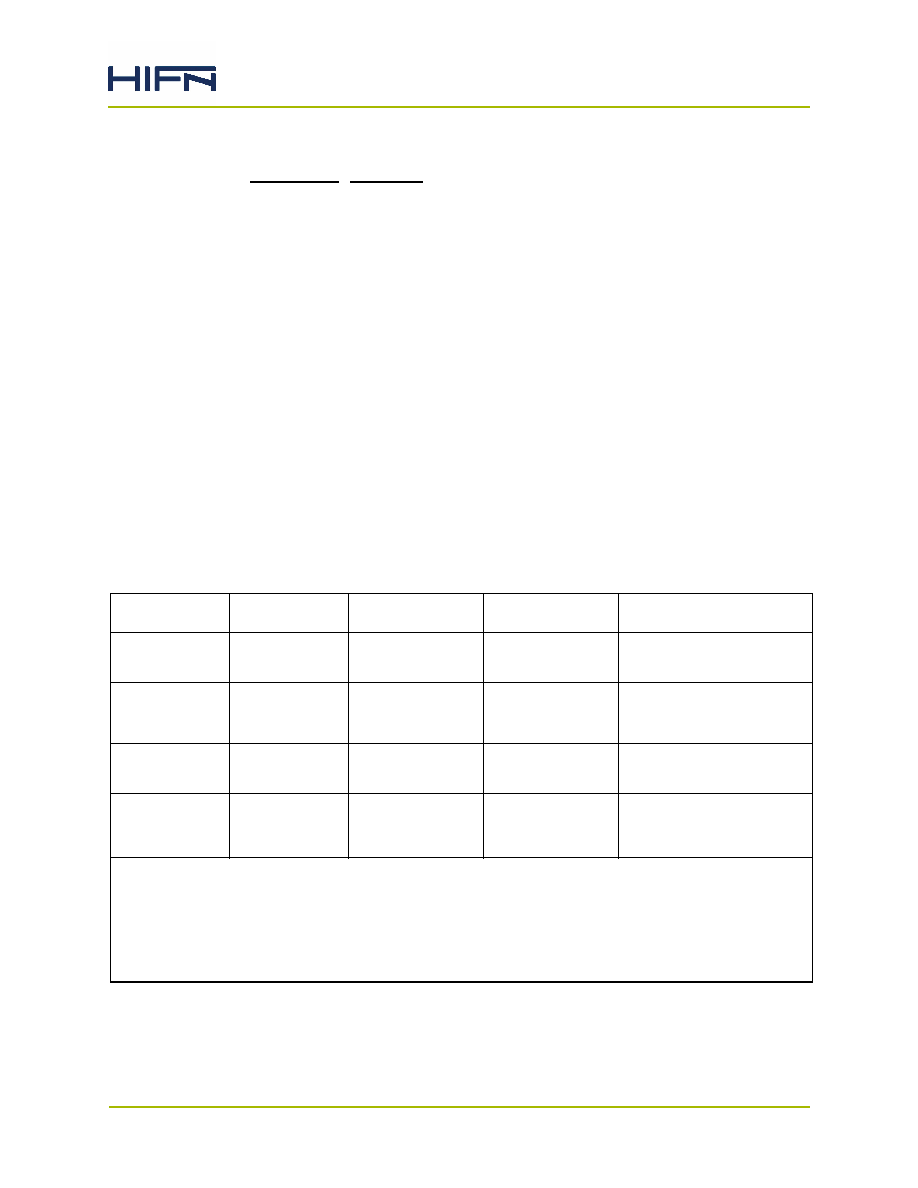

Table 5-1. Boot Process Summary

dpu_gpio[1]/

boot_config_1

dpu_gpio[0] /

boot_config_0

DPU Boots from:

eSC Boots from:

Comments

00

Host 0/1 GMAC

or eSC inter-

connect bus

RMII port or

DPU inter-

connect bus

Normal system

No Flash

01

eSC inter-

connect bus only

(No GMAC)

RMII port.

FIPS-140 secure system

boot1

No flash

10

Flash Fail to

Host GMAC or

eSC

Flash. Fail to

DPU or RMII

Normal system

With Flash2

11

Flash Fail to eSC

Only (No Host

GMAC boot)

Flash Fail to DPU

or RMII

FIPS-140 secure system

boot1

With Flash2

Note

1. A secure system boot is referring to a design where it is required to carefully control where the

bootload software image comes from (such as in a FIPS-140 design). In such a system, a design may

utilize a secure control processor attached to the RMII port for bootload and device management. These

boot pin settings will not allow a boot image to be delivered over the GMAC host (or network) ports.

Contact Hifn for availability of software support for this feature.

2. The SDRAM must be populated.

相关PDF资料 |

PDF描述 |

|---|---|

| 4450HA/3-K | MICROPROCESSOR, PBGA324 |

| 45-21/LK2C-B56702C4CB2/2T | SINGLE COLOR LED, COOL WHITE |

| 45-21/LK2C-B38452C4CB2/2T | SINGLE COLOR LED, WARM WHITE |

| 45-21/QK2C-B45562C4CB2/2T | SINGLE COLOR LED, COOL WHITE |

| 45-21/QK2C-B56702C4CB41/2T | SINGLE COLOR LED, COOL WHITE |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 445-0X | 制造商:APEX 功能描述:TOOLS, HEX BITS; Bit Type:Slotted; Hex Bit Size:3F-4R; Length:25mm; Size:1" ;RoHS Compliant: NA |

| 4451 | 功能描述:电缆固定件和配件 PG 7 HYBRID CG .87X.59 .12-.28 RoHS:否 制造商:Heyco 类型:Cable Grips, Liquid Tight 材料:Nylon 颜色:Black 安装方法:Cable 最大光束直径:11.4 mm 抗拉强度: |

| 44510 | 功能描述:钳子和镊子 ESD Safe Tweezers 7a SA - 120mm RoHS:否 制造商:OK Industries 大小: 类型:Insertion/Extraction Tools And Kit |

| 44-510 | 制造商:RAWLPLUG 功能描述:RAWLBOLT PROJECTING M625P |

| 445100170 | 制造商:OMRON AUTOMATION AND SAFETY 功能描述:SR10 24VAC/DC OR 110/220VAC |

发布紧急采购,3分钟左右您将得到回复。