- 您现在的位置:买卖IC网 > PDF目录157285 > 5V19EE904NLGI (INTEGRATED DEVICE TECHNOLOGY INC) 5V SERIES, PLL BASED CLOCK DRIVER, 7 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), QCC32 PDF资料下载

参数资料

| 型号: | 5V19EE904NLGI |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 5V SERIES, PLL BASED CLOCK DRIVER, 7 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), QCC32 |

| 封装: | 0.50 MM PITCH, ROHS COMPLIANT, VFQFPN-32 |

| 文件页数: | 18/29页 |

| 文件大小: | 292K |

| 代理商: | 5V19EE904NLGI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

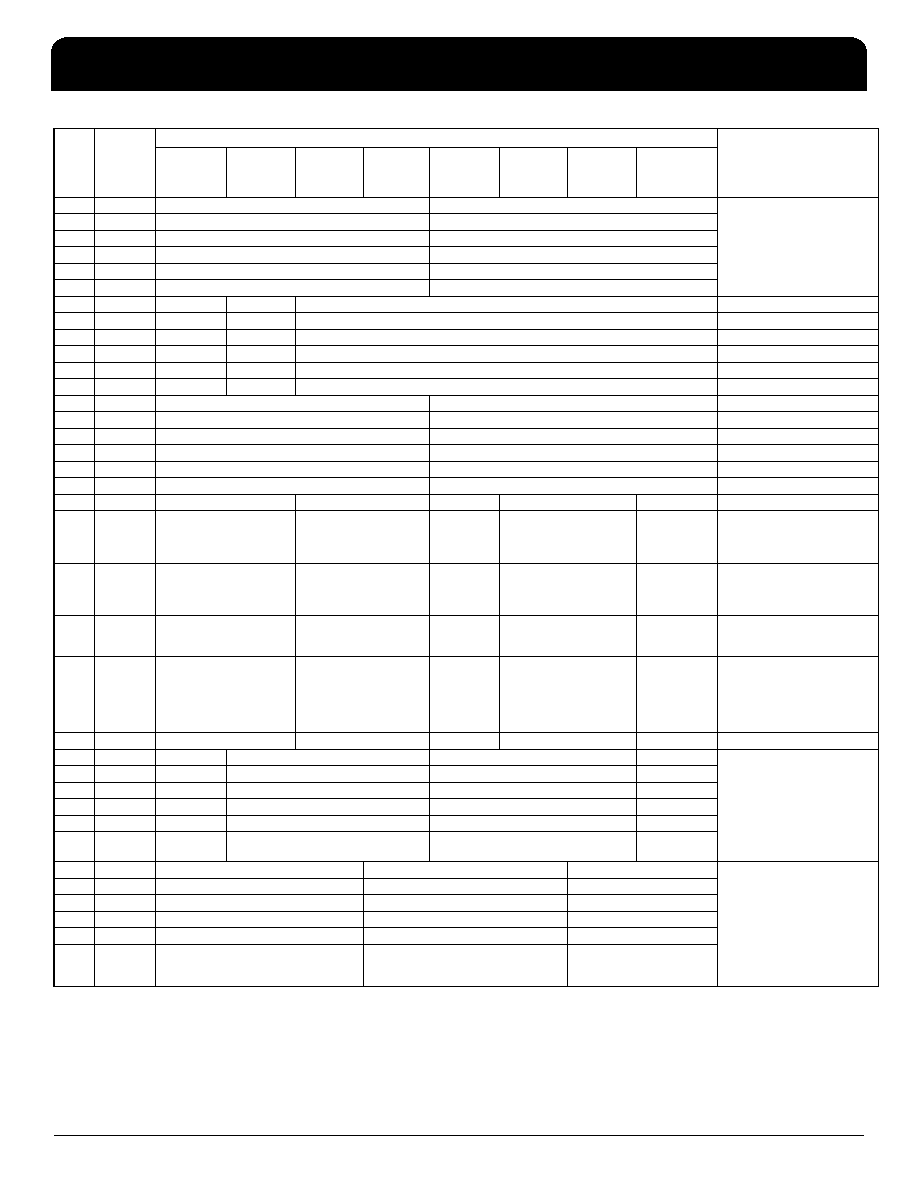

IDT5V19EE904

EEPROM PROGRAMMABLE VCXO CLOCK GENERATOR

CLOCK SYNTHESIZER

IDT EEPROM PROGRAMMABLE VCXO CLOCK GENERATOR

25

IDT5V19EE904

REV H 042211

Default Configuration: OUT1 = Reference Clock output, all

other outputs turned off.

0xAC

00

TSSC[3:0]_CFG0

NSSC[3:0]_CFG0

PLL0 Spread Spectrum Control

0xAD

00

TSSC[3:0]_CFG1

NSSC[3:0]_CFG1

0xAE

00

TSSC[3:0]_CFG2

NSSC[3:0]_CFG2

0xAF

00

TSSC[3:0]_CFG3

NSSC[3:0]_CFG3

0xB0

00

TSSC[3:0]_CFG4

NSSC[3:0]_CFG4

0xB1

00

TSSC[3:0]_CFG5

NSSC[3:0]_CFG5

0xB2

00

DITH_CFG4

X2_CFG4

SSOFFSET[5:0]_CFG4

0xB3

00

DITH_CFG5

X2_CFG5

SSOFFSET[5:0]_CFG5

0xB4

00

DITH_CFG0

X2_CFG0

SSOFFSET[5:0]_CFG0

0xB5

00

DITH_CFG1

X2_CFG1

SSOFFSET[5:0]_CFG1

0xB6

00

DITH_CFG2

X2_CFG2

SSOFFSET[5:0]_CFG2

0xB7

00

DITH_CFG3

X2_CFG3

SSOFFSET[5:0]_CFG3

0xB8

11

SD1[3:0]_CFG0

SD0[3:0]_CFG0

0xB9

11

SD1[3:0]_CFG1

SD0[3:0]_CFG1

0xBA

11

SD1[3:0]_CFG2

SD0[3:0]_CFG2

0xBB

11

SD1[3:0]_CFG3

SD0[3:0]_CFG3

0xBC

11

SD1[3:0]_CFG4

SD0[3:0]_CFG4

0xBD

11

SD1[3:0]_CFG5

SD0[3:0]_CFG5

0xBE

AE

SRC1[1:0]_CFG4

SRC0[1:0]_CFG4

PDPL3_CFG4

SM[1:0]_CFG4

PRIMSRC_CFG4 Output Divide Source Selection

0xBF

AE

SRC1[1:0]_CFG5

SRC0[1:0]_CFG5

PDPL3_CFG5

SM[1:0]_CFG5

PRIMSRC_CFG5

PRIMSRC - primary source -

crystal or ICLOCK

0 = crystal/REFIN

1 = CLKIN

0xC0

AE

SRC1[1:0]_CFG0

SRC0[1:0]_CFG0

PDPL3_CFG0

SM[1:0]_CFG0

PRIMSRC_CFG0

SM = switch mode

0x = manual

10 = reserved

11 = auto-revertive

0xC1

AE

SRC1[1:0]_CFG1

SRC0[1:0]_CFG1

PDPL3_CFG1

SM[1:0]_CFG1

PRIMSRC_CFG1 PDPL3 - PLL3 shutdown

0 = normal

1 = shut down

0xC2

AE

SRC1[1:0]_CFG2

SRC0[1:0]_CFG2

PDPL3_CFG2

SM[1:0]_CFG2

PRIMSRC_CFG2 SRC = MUX control bit prior to

DIV#

SRC0[1:0]

00 - DIV1

01 - DIV3

10 - Reference input

0xC3

AE

SRC1[1:0]_CFG3

SRC0[1:0]_CFG3

PDPL3_CFG3

SM[1:0]_CFG3

PRIMSRC_CFG3

0xC4

24

SRC4[0]_CFG0

SRC3[2:0]_CFG0

SRC2[2:0]_CFG0

SRC1[2]_CFG0

SRC1/SRC2/SRC3.SRC5

000 - DIV1

001 - DIV3

010 - Reference input

011 - Reserved

100 - PLL0

101 - PLL1

110 - PLL2

111 - PLL3

0xC5

24

SRC4[0]_CFG1

SRC3[2:0]_CFG1

SRC2[2:0]_CFG1

SRC1[2]_CFG1

0xC6

24

SRC4[0]_CFG2

SRC3[2:0]_CFG2

SRC2[2:0]_CFG2

SRC1[2]_CFG2

0xC7

24

SRC4[0]_CFG3

SRC3[2:0]_CFG3

SRC2[2:0]_CFG3

SRC1[2]_CFG3

0xC8

24

SRC4[0]_CFG4

SRC3[2:0]_CFG4

SRC2[2:0]_CFG4

SRC1[2]_CFG4

0xC9

24

SRC4[0]_CFG5

SRC3[2:0]_CFG5

SRC2[2:0]_CFG5

SRC1[2]_CFG5

0xCA

49

SRC6[2:0]_CFG4

SRC5[2:0]_CFG4

SRC4[2:1]_CFG4

SRC6

000 - Reserved

001 - Reserved

010 - Reference input

011 - Reserved

100 - Reserved

101 - PLL1

110 - Reserved

111 - Reserved

Quiet MUX

0xCB

49

SRC6[2:0]_CFG5

SRC5[2:0]_CFG5

SRC4[2:1]_CFG5

0xCC

49

SRC6[2:0]_CFG0

SRC5[2:0]_CFG0

SRC4[2:1]_CFG0

0xCD

49

SRC6[2:0]_CFG1

SRC5[2:0]_CFG1

SRC4[2:1]_CFG1

0xCE

49

SRC6[2:0]_CFG2

SRC5[2:0]_CFG2

SRC4[2:1]_CFG2

0xCF

49

SRC6[2:0]_CFG3

SRC5[2:0]_CFG3

SRC4[2:1]_CFG3

Addr

Default

Register

Hex

Value

Bit #

Description

76

5

4

3

2

1

0

相关PDF资料 |

PDF描述 |

|---|---|

| 5V60014DVGI8 | PLL BASED CLOCK DRIVER, PDSO8 |

| 6.0MHZ12SMX-B20100075FUNDTR | QUARTZ CRYSTAL RESONATOR, 6 MHz |

| 6.0MHZ12SMX-C201002010FUNDTR | QUARTZ CRYSTAL RESONATOR, 6 MHz |

| 6.0MHZ12SMX-B201000SRFUNDTR | QUARTZ CRYSTAL RESONATOR, 6 MHz |

| 6.0MHZ12SMX-C1001004075FUNDTR | QUARTZ CRYSTAL RESONATOR, 6 MHz |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5V19EE904NLGI8 | 功能描述:时钟发生器及支持产品 EEPROM PROGRAMMABLE PLL AND VCXO RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| 5V1A-ADAPTER | 制造商:Distributed By MCM 功能描述:5V 1A Switching AC Power Supply - Micro USB |

| 5V1A-USB | 制造商:Gravitech 功能描述:USB WALL ADAPTER 5V 1A |

| 5V1BC | 制造商:SEMTECH_ELEC 制造商全称:SEMTECH ELECTRONICS LTD. 功能描述:Silicon Epitaxial Planar Zener Diodes |

| 5V1BCA | 制造商:SEMTECH_ELEC 制造商全称:SEMTECH ELECTRONICS LTD. 功能描述:Silicon Epitaxial Planar Zener Diodes |

发布紧急采购,3分钟左右您将得到回复。