- 您现在的位置:买卖IC网 > PDF目录20606 > 71M6543F-IGTR/F (Maxim Integrated)IC ENERGY METER 64K FLSH 100LQFP PDF资料下载

参数资料

| 型号: | 71M6543F-IGTR/F |

| 厂商: | Maxim Integrated |

| 文件页数: | 111/154页 |

| 文件大小: | 0K |

| 描述: | IC ENERGY METER 64K FLSH 100LQFP |

| 标准包装: | 1,000 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页当前第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页

�� �

�

�

�71M6543F/71M6543G� Data� Sheet�

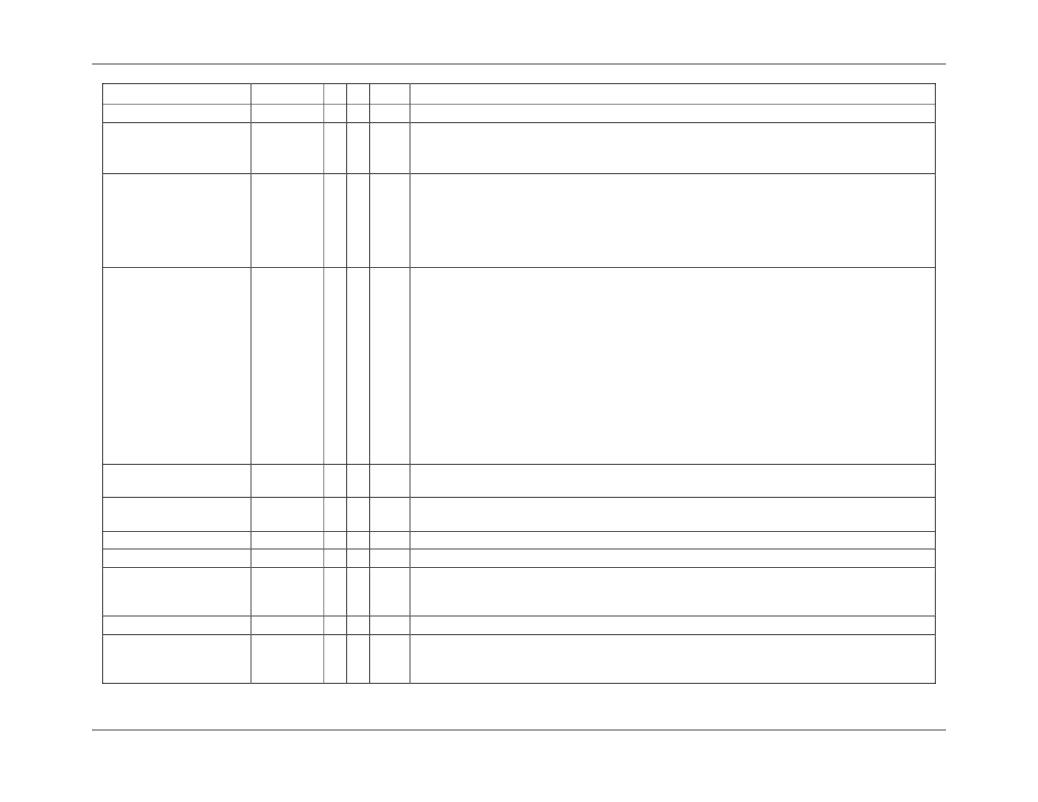

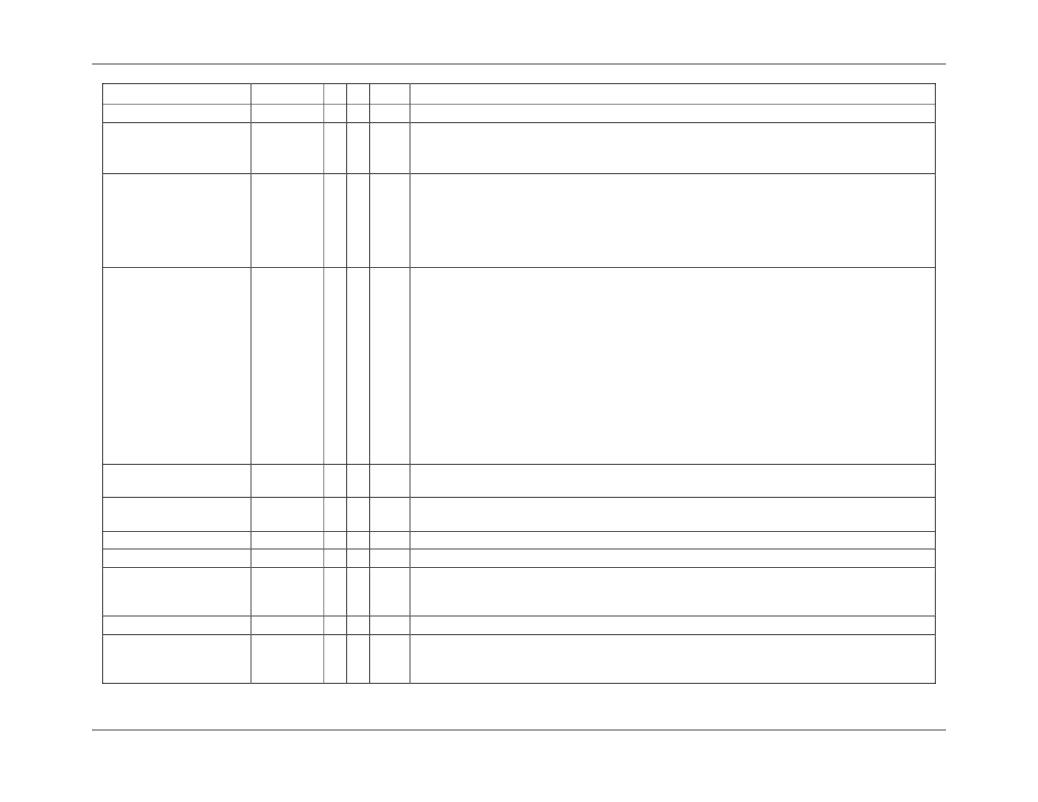

�Name�

�Location� Rst Wk� Dir�

�Description�

�PLL_OK�

�PLL_FAST�

�SFR� F9[4]�

�2200[4]�

�0�

�0�

�0�

�0�

�R�

�R/W�

�Indicates� that� the� clock� generation� PLL� is� settled.�

�Controls� the� speed� of� the� PLL� and� MCK.�

�1� =� 19.66� MHz� (XTAL� *� 600)�

�0� =� 6.29� MHz� (XTAL� *� 192)�

�PLS_MAXWIDTH[7:0]�

�210A[7:0]� FF� FF� R/W�

�PLS_MAXWIDTH[7:0]� determines� the� maximum� width� of� the� pulse� (low-going� pulse� if�

�PLS_INV� =0� or� high-going� pulse� if� PLS_INV� =1).� The� maximum� pulse� width� is�

�(2*� PLS_MAXWIDTH[7:0]� +� 1)*T� I� .� Where� T� I� is� PLS_INTERVAL[7:0]� in� units� of� CK_FIR�

�clock� cycles.� If� PLS_INTERVAL[7:0]� =� 0� or� PLS_MAXWIDTH[7:0]� =� 255,� no� pulse�

�width� checking� is� performed� and� the� output� pulses� have� 50%� duty� cycle.� See� 2.3.6.2�

�VPULSE� and� WPULSE� .�

�PLS_INTERVAL[7:0]�

�PLS_INV�

�PORT_E�

�PRE_E�

�PREBOOT�

�210B[7:0]�

�210C[0]�

�270C[5]�

�2704[5]�

�SFRB2[7]�

�0�

�0�

�0�

�0�

�–�

�0�

�0�

�0�

�0�

�–�

�R/W�

�R/W�

�R/W�

�R/W�

�R�

�PLS_INTERVAL[7:0]� determines� the� interval� time� between� pulses.� The� time� between�

�output� pulses� is� PLS_INTERVAL[7:0]� *4� in� units� of� CK_FIR� clock� cycles.� If�

�PLS_INTERVAL[7:0]� =� 0,� the� FIFO� is� not� used� and� pulses� are� output� as� soon� as� the� CE�

�issues� them.� PLS_INTERVAL[7:0]� is� calculated� as� follows:�

�PLS_INTERVAL[7:0]� =� Floor� (� Mux� frame� duration� in� CK_FIR� cycles� /� CE� pulse� updates� per� Mux�

�frame� /� 4� )�

�For� example,� since� the� 71M6543� CE� code� is� written� to� generate� 6� pulses� in� one� integration�

�interval,� when� the� FIFO� is� enabled� (i.e.,� PLS_INTERVAL[7:0]� ≠� 0)� and� that� the� frame�

�duration� is� 1950� CK_FIR� clock� cycles,� PLS_INTERVAL[7:0]� should� be� written� with�

�Floor(1950� /� 6� /� 4)� =� 81� so� that� the� five� pulses� are� evenly� spaced� in� time� over� the�

�integration� interval� and� the� last� pulse� is� issued� just� prior� to� the� end� of� the� interval.� See�

�2.3.6.2� VPULSE� and� WPULSE� .�

�Inverts� the� polarity� of� WPULSE,� VARPULSE,� XPULSE,� and� YPULSE.� Normally,� these�

�pulses� are� active� low.� When� inverted,� they� become� active� high.�

�Enables� outputs� from� the� SEGDIO0-SEGDIO15� pins.� PORT_E� =� 0� blocks� the� momentary�

�output� pulse� that� occurs� when� SEGDIO0-SEGDIO15� are� reset� on� power-up.�

�Enables� the� 8x� pre-amplifier.�

�Indicates� that� pre-boot� sequence� is� active.�

�RCMD[4:0]�

�SFR� FC[4:0]� 0�

�0�

�R/W�

�When� the� MPU� writes� a� non-zero� value� to� RCMD� ,� the� 71M6543� issues� a� command� to�

�the� appropriate� remote� sensor.� When� the� command� is� complete,� the� 71M6543� clears�

�RCMD.�

�RESET�

�RFLY_DIS�

�2200[3]�

�210C[3]�

�0�

�0�

�0�

�0�

�W�

�R/W�

�When� set,� writes� a� one� to� WF_RSTBIT� and� then� causes� a� reset.�

�Controls� how� the� 71M6543� drives� the� power� pulse� for� the� 71M6xxx.� When� set,� the�

�power� pulse� is� driven� high� and� low.� When� cleared,� it� is� driven� high� followed� by� an� open�

�circuit� fly-back� interval.�

�v2�

�111�

�相关PDF资料 |

PDF描述 |

|---|---|

| R1S-0524/HP | CONV DC/DC 1W 05VIN 24VOUT |

| SS10P3CL-M3/87A | DIODE SCHOTTKY 10A 30V SMPC |

| ISL6549CRZ | IC REG DL BCK/LINEAR SYNC 16-QFN |

| ISL6549IRZ-T | IC REG DL BCK/LINEAR SYNC 16-QFN |

| AMC40DRTF | CONN EDGECARD 80POS .100 DIP SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 71M6543FT-IGT/F | 制造商:Maxim Integrated Products 功能描述:ENERGY METER ICS - Rail/Tube |

| 71M6543FT-IGTR/F | 制造商:Maxim Integrated Products 功能描述:3-PHASE SOC, 64KB FLASH, PRES TEMP SENSOR - Tape and Reel |

| 71M6543G | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Selectable Gain of 1 or 8 for One Current Energy Meter ICs Metrology Compensation |

| 71M6543GH | 制造商:未知厂家 制造商全称:未知厂家 功能描述:电表IC |

| 71M6543GHT-IGT/F | 制造商:Maxim Integrated Products 功能描述:3-PHASE, 128KB, PRES TEMP SENSOR, HI PREC - Bulk |

发布紧急采购,3分钟左右您将得到回复。