- 您现在的位置:买卖IC网 > PDF目录20606 > 71M6543F-IGTR/F (Maxim Integrated)IC ENERGY METER 64K FLSH 100LQFP PDF资料下载

参数资料

| 型号: | 71M6543F-IGTR/F |

| 厂商: | Maxim Integrated |

| 文件页数: | 69/154页 |

| 文件大小: | 0K |

| 描述: | IC ENERGY METER 64K FLSH 100LQFP |

| 标准包装: | 1,000 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页当前第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页

�� �

�

�

�71M6543F/71M6543G� Data� Sheet�

�SPI� Safe� Mode�

�Sometimes� it� is� desirable� to� prevent� the� SPI� interface� from� writing� to� arbitrary� RAM� locations� and� thus�

�disturbing� MPU� and� CE� operation.� This� is� especially� true� in� AFE� applications.� For� this� reason,� the� SPI�

�SAFE� mode� was� created.� In� SPI� SAFE� mode,� SPI� write� operations� are� disabled� except� for� a� 16� byte�

�transfer� region� at� address� 0x400� to� 0x40F.� If� the� SPI� host� needs� to� write� to� other� addresses,� it� must� use�

�the� SPI_CMD� register� to� request� the� write� operation� from� the� MPU.� SPI� SAFE� mode� is� enabled� by� the�

�SPI_SAFE� bit� (I/O� RAM� 0x270C[3])� .�

�Single-Byte� Transaction�

�If� a� transaction� is� a� single� byte,� the� byte� is� interpreted� as� SPI_CMD.� Regardless� of� the� byte� value,�

�single-byte� transactions� always� update� the� SPI_CMD� register� and� cause� an� SPI� interrupt� to� be� generated.�

�Multi-Byte� Transaction�

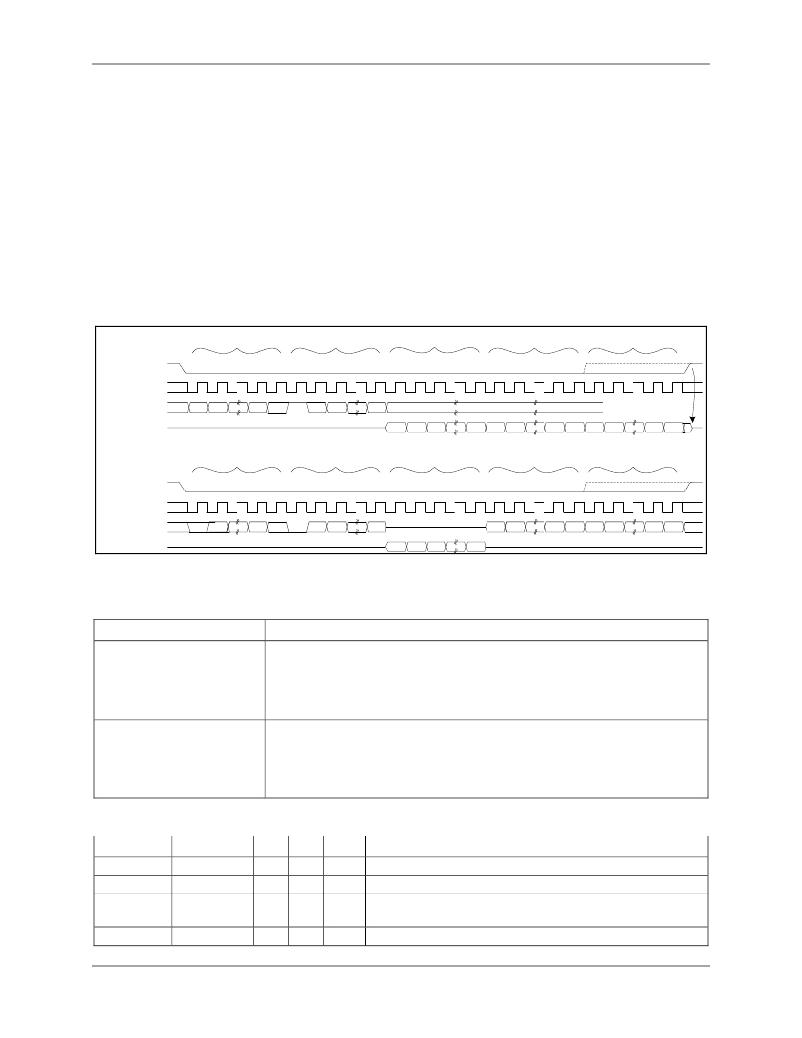

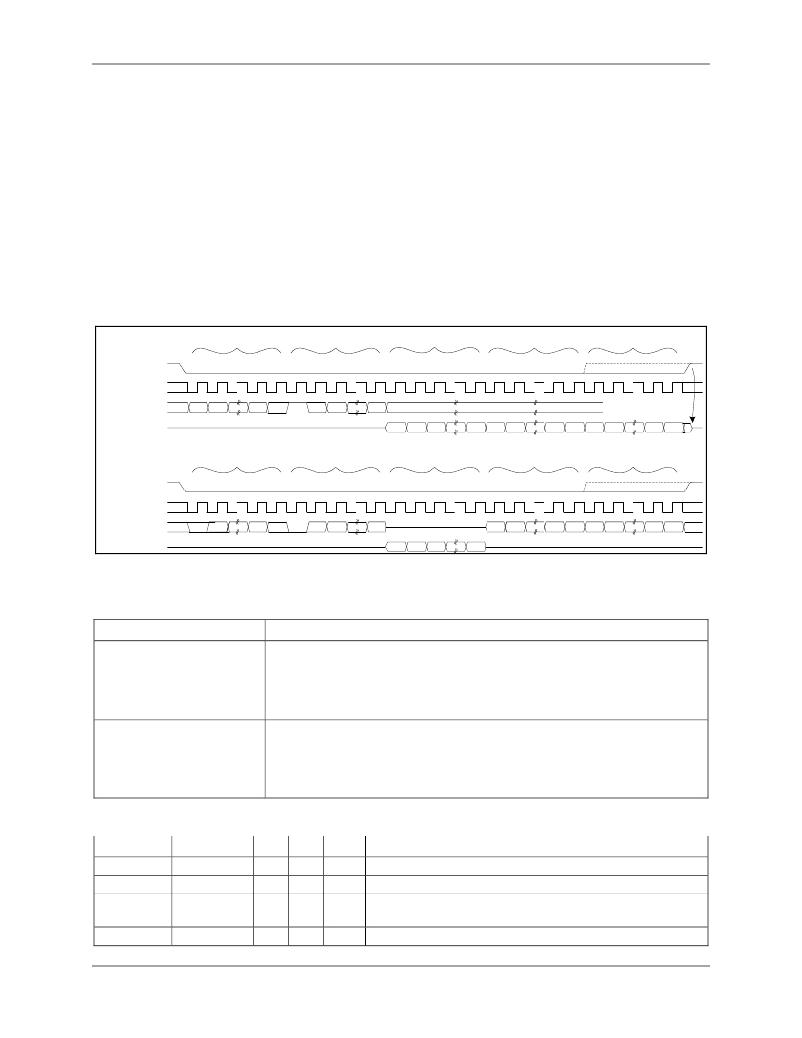

�As� shown� in� Figure� 23� ,� multi-byte� operations� consist� of� a� 16� bit� address� field,� an� 8� bit� CMD,� a� status� byte,�

�and� a� sequence� of� data� bytes.� A� multi� byte� transaction� is� three� or� more� bytes.�

�SERIAL� READ�

�16� bit� Address�

�8� bit� CMD�

�Status� Byte�

�DATA[ADDR]�

�DATA[ADDR+1]�

�(From� Host)� SPI_CSZ�

�Extended� Read� .� .� .�

�0�

�15�

�16�

�23�

�24�

�31�

�32�

�39�

�40�

�47�

�(From� Host)� SPI_CK�

�(From� Host)� SPI_DI�

�A15�

�A14�

�A1�

�A0�

�C7�

�C6�

�C5�

�C0�

�x�

�(From� 6543)� SPI_DO�

�HI� Z�

�ST7�

�ST6�

�ST5�

�ST0�

�D7�

�D6�

�D1�

�D0�

�D7�

�D6�

�D1�

�D0�

�SERIAL� WRITE�

�16� bit� Address�

�8� bit� CMD�

�Status� Byte�

�DATA[ADDR]�

�DATA[ADDR+1]�

�(From� Host)� SPI_CSZ�

�Extended� Write� .� .� .�

�0�

�15�

�16�

�23�

�24�

�31�

�32�

�39�

�40�

�47�

�(From� Host)� SPI_CK�

�(From� Host)� SPI_DI�

�x�

�A15�

�A14�

�A1�

�A0�

�C7�

�C6�

�C5�

�C0�

�D7�

�D6�

�D1�

�D0�

�D7�

�D6�

�D1�

�D0�

�x�

�(From� 6543)� SPI_DO�

�HI� Z�

�ST7�

�ST6�

�ST5�

�ST0�

�Figure� 23:� SPI� Slave� Port� -� Typical� Multi-Byte� Read� and� Write� operations�

�Table� 57:� SPI� Command� Sequences�

�Command� Sequence�

�ADDR� 1xxx� xxxx� STATUS�

�Byte0� ...� ByteN�

�ADDR� 0xxx� xxxx� STATUS�

�Byte0� ...� ByteN�

�Description�

�Read� data� starting� at� ADDR.� ADDR� is� auto-incremented� until� SPI_CSZ�

�is� raised.� Upon� completion,� SPI_CMD� (� SFR� 0xFD� )� is� updated� to� 1xxx� xxxx�

�and� an� SPI� interrupt� is� generated.� The� exception� is� if� the� command�

�byte� is� 1000� 0000.� In� this� case,� no� MPU� interrupt� is� generated� and�

�SPI_CMD� is� not� updated.�

�Write� data� starting� at� ADDR.� ADDR� is� auto-incremented� until� SPI_CSZ� is�

�raised.� Upon� completion,� SPI_CMD� is� updated� to� 0xxx� xxxx� and� an� SPI�

�interrupt� is� generated.� The� exception� is� if� the� command� byte� is� 0000�

�0000.� In� this� case,� no� MPU� interrupt� is� generated� and� SPI_CMD� is� not�

�updated.�

�Table� 58:� SPI� Registers�

�Name�

�EX_SPI�

�SPI_CMD�

�SPI_E�

�IE_SPI�

�Location�

�2701[7]�

�SFR FD[7:0]�

�270C[4]�

�SFR� F8[7]�

�Rst�

�0�

�–�

�1�

�0�

�Wk�

�0�

�–�

�1�

�0�

�Dir�

�R/W�

�R�

�R/W�

�R/W�

�Description�

�SPI� interrupt� enable� bit.�

�SPI� command.� The� 8-bit� command� from� the� bus� master.�

�SPI� port� enable� bit.� It� enables� the� SPI� interface� on� pins�

�SEGDIO36� –� SEGDIO39.�

�SPI interrupt flag. Set by hardware, cleared by writing a 0.�

�v2�

�69�

�相关PDF资料 |

PDF描述 |

|---|---|

| R1S-0524/HP | CONV DC/DC 1W 05VIN 24VOUT |

| SS10P3CL-M3/87A | DIODE SCHOTTKY 10A 30V SMPC |

| ISL6549CRZ | IC REG DL BCK/LINEAR SYNC 16-QFN |

| ISL6549IRZ-T | IC REG DL BCK/LINEAR SYNC 16-QFN |

| AMC40DRTF | CONN EDGECARD 80POS .100 DIP SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 71M6543FT-IGT/F | 制造商:Maxim Integrated Products 功能描述:ENERGY METER ICS - Rail/Tube |

| 71M6543FT-IGTR/F | 制造商:Maxim Integrated Products 功能描述:3-PHASE SOC, 64KB FLASH, PRES TEMP SENSOR - Tape and Reel |

| 71M6543G | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Selectable Gain of 1 or 8 for One Current Energy Meter ICs Metrology Compensation |

| 71M6543GH | 制造商:未知厂家 制造商全称:未知厂家 功能描述:电表IC |

| 71M6543GHT-IGT/F | 制造商:Maxim Integrated Products 功能描述:3-PHASE, 128KB, PRES TEMP SENSOR, HI PREC - Bulk |

发布紧急采购,3分钟左右您将得到回复。