- 您现在的位置:买卖IC网 > PDF目录16271 > 78Q8430EBST#DB (Maxim Integrated Products)EVAL BOARD 78Q8430 PDF资料下载

参数资料

| 型号: | 78Q8430EBST#DB |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 24/88页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD 78Q8430 |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页

78Q8430 Data Sheet

DS_8430_001

30

Rev. 1.2

Snooping the contents of a frame before it is read out of the receive QUE can be useful if additional

inspection of the frame is needed, beyond what is provided by classification, to determine the disposition

of a received frame. It can also be used, in conjunction with the QUE transfer feature, to minimize host

bus overhead in responding to simple ARP or ICMP requests. In this case, the host can use the Snoop

Interface to modify a received ARP or ICMP request and convert it into the appropriate response, while

the frame is still resident in the receive QUE. The QUE Transfer feature is then used to transfer the

response directly to a TX QUE and transmit it back to the source without having to read the entire frame

into host memory.

6.5

Water Marking

The Timers module (see Section 6.8) monitors the number of free memory blocks in the system input.

There are three watermarks (Interrupt, PAUSE and Headroom), accessed via the Water Mark Values

Register (WMVR), which can be used to manage memory usage based on the size of the free memory pool.

6.5.1

Interrupt Watermark

When the number of free BLOCKs falls below the interrupt threshold, the WATER MARK interrupt in the

HIR is triggered. An interrupt threshold setting of zero disables this feature.

6.5.2

PAUSE Watermark

When the number of free BLOCKs falls below the pause threshold, the QDR bit for the PAUSE QUE

triggers the transmission of the pause frame. A pause threshold setting of zero disables this feature.

6.5.3

Headroom Watermark

When the number of free BLOCKs falls below the headroom threshold then the MAC receiver is halted

causing the MAC to drop any frames received after completion of the current frame. This condition is

cleared once the number of free BLOCKs rises back above the threshold. This prevents a saturated

receiver from consuming all free memory thereby locking out the local transmitter. A headroom setting of

zero disables this feature.

6.6

Counters

A block of hardware counters is implemented to allow monitoring transmit and receive statistics. These

counters are accessed and managed by using the Count Data Register (CDR), the Counter Control

6.6.1

Summary of Counters

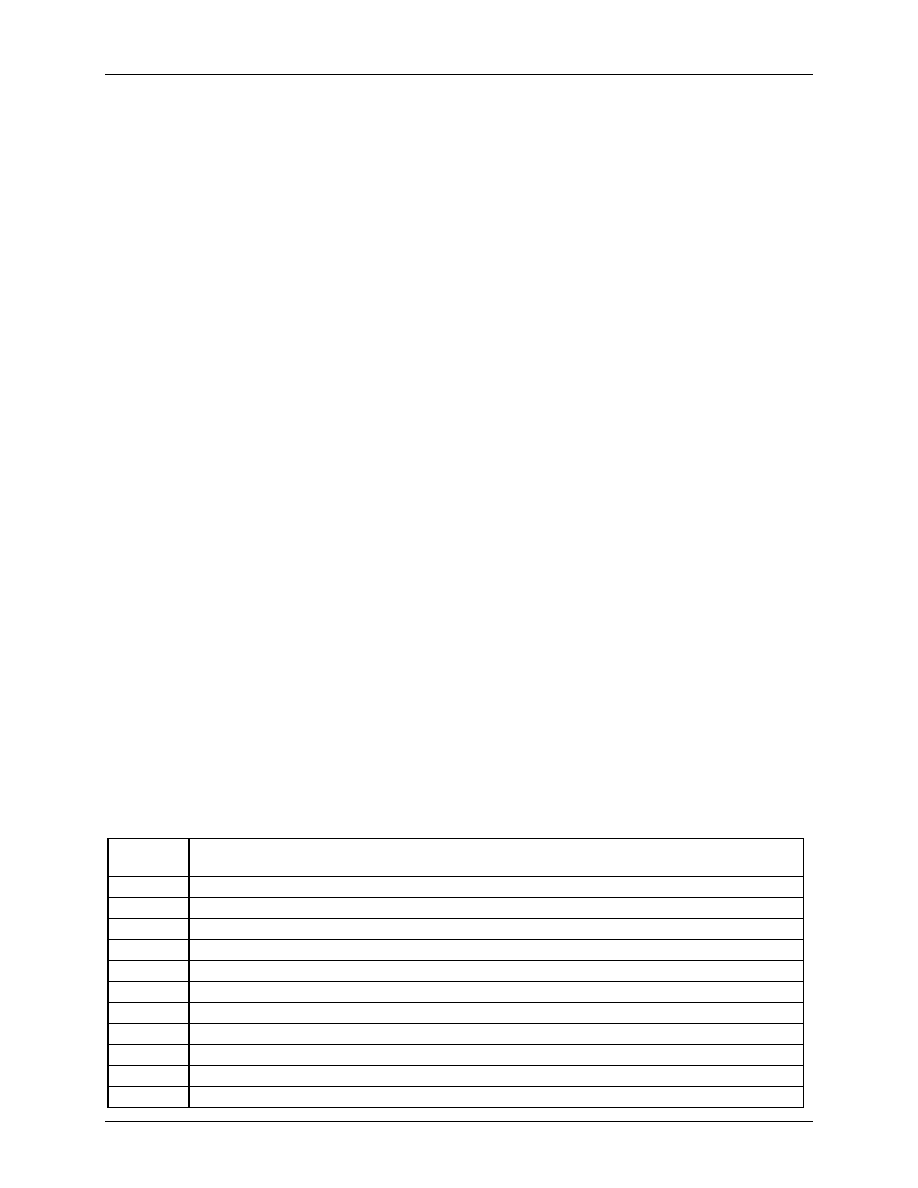

Table 23 provides a summary of all counters by address. Counters at addresses 0x00 through 0x0E are

transmit counters. Counters at addresses 0x0F through 0x27 are receive counters.

Table 23: Counter Summary

Counter

Address

Counter Description

0x00

Transmitted Packets, 0 Collisions, not deferred or excessive deferred

0x01

Transmitted Packets, 1 Collision

0x02

Transmitted Packets, 2-15 Collisions

0x03

Excessive Collisions

0x04

Deferred transmissions

0x05

Late Collisions

0x06

MAC errors (TX under-run or transmit halted)

0x07

Lost carrier sense errors

0x08

Excessive deferrals

0x09

Total packets transmitted

0x0A

Multicast packets

相关PDF资料 |

PDF描述 |

|---|---|

| CM453232-R18KL | INDUCTOR 180NH 700MA SMD |

| REC15-1205D/H3 | CONV DC/DC 15W 12VIN +/-05VOUT |

| VI-JWL-EZ-F3 | CONVERTER MOD DC/DC 28V 25W |

| A3BKB-2406G | IDC CABLE- ASR24B/AE24G/APK24B |

| REC15-2415D/H3 | CONV DC/DC 15W 24VIN +/-15VOUT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 78Q8430STEM#DB | 功能描述:以太网开发工具 3-in-1 Silicon Delay Line RoHS:否 制造商:Micrel 产品:Evaluation Boards 类型:Ethernet Transceivers 工具用于评估:KSZ8873RLL 接口类型:RMII 工作电源电压: |

| 78-R3 | 功能描述:3M SCOTCHCAST REENTERABLE SIGNAL 制造商:3m 系列:* 零件状态:在售 标准包装:1 |

| 78-R4 | 功能描述:3M SCOTCHCAST REENTERABLE SIGNAL 制造商:3m 系列:* 零件状态:在售 标准包装:1 |

| 78RB02 | 功能描述:SWITCH 2 POS DIP RECESSED UNSLD RoHS:否 类别:开关 >> DIP 系列:78 特色产品:RDM Series Rotary DIP Switch 标准包装:70 系列:RDM 电路:十六进制 位置数:16 触点额定电压:0.1A @ 42VDC 触动器类型:用于工具旋转 触动器电平:凹槽式 安装类型:通孔 方向:顶部触动 可清洗:是 其它名称:EG4977-5RDMAR16PIT |

| 78RB02RA | 制造商:Grayhill 功能描述:DIP, 2 POS, FLUSH ACTUATOR, SPST, GOLD - Rail/Tube |

发布紧急采购,3分钟左右您将得到回复。