参数资料

| 型号: | AD5757ACPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 42/44页 |

| 文件大小: | 0K |

| 描述: | IC DAC 16BIT QUAD 64-LFCSP |

| 特色产品: | AD5755 / AD5755-1 / AD5757 DACs |

| 标准包装: | 1 |

| 设置时间: | 15µs |

| 位数: | 16 |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 4 |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 管件 |

| 输出数目和类型: | * |

| 采样率(每秒): | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页当前第42页第43页第44页

Data Sheet

AD5757

Rev. D | Page 7 of 44

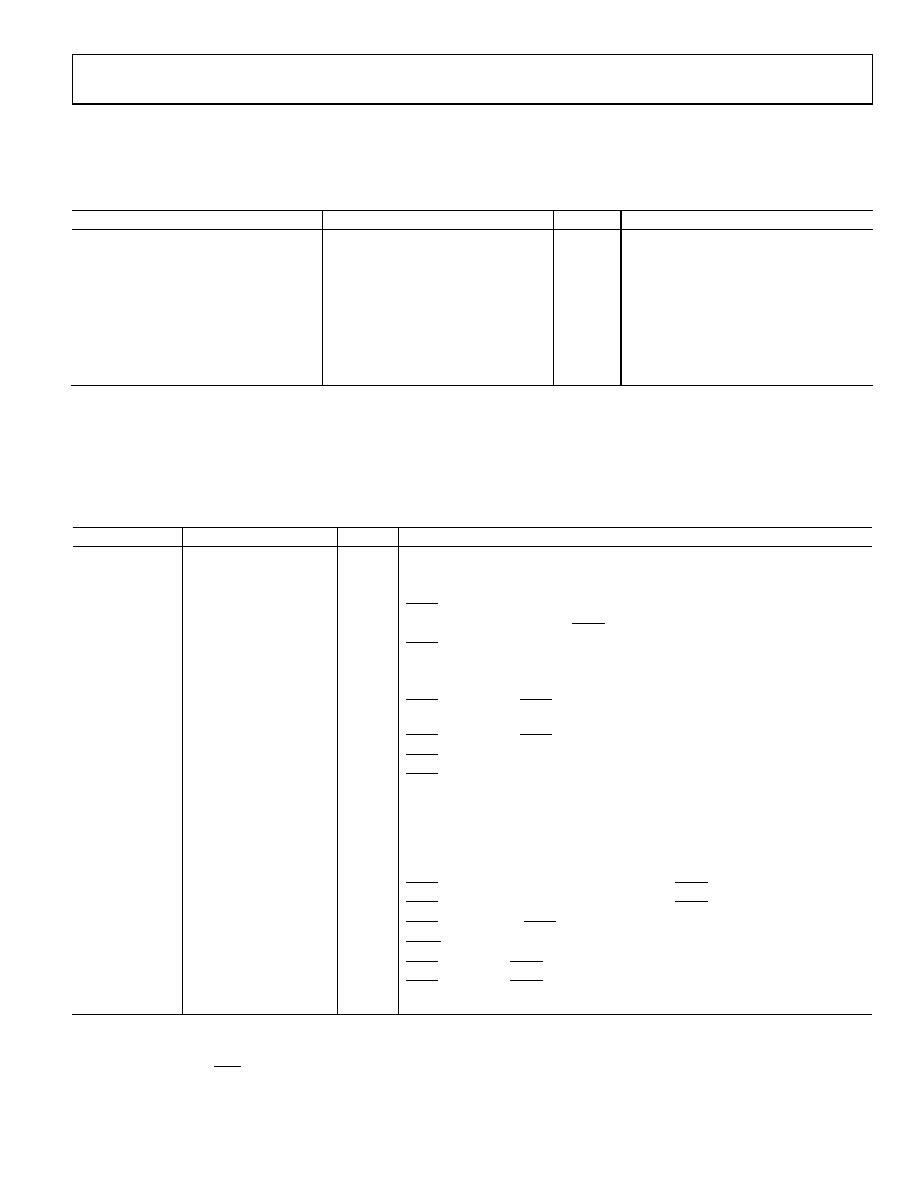

AC PERFORMANCE CHARACTERISTICS

AVDD = VBOOST_x = 15 V; DVDD = 2.7 V to 5.5 V; AVCC = 4.5 V to 5.5 V; dc-to-dc converter disabled; AGND = DGND = GNDSWx = 0 V;

REFIN = 5 V; RL = 300 ; all specifications TMIN to TMAX, unless otherwise noted.

Table 2.

Parameter1

Min

Typ

Max

Unit

Test Conditions/Comments

DYNAMIC PERFORMANCE

Current Output

Output Current Settling Time

15

s

To 0.1% FSR (0 mA to 24 mA)

See test conditions/

comments

ms

Output Noise (0.1 Hz to 10 Hz

Bandwidth)

0.15

LSB p-p

16-bit LSB, 0 mA to 24 mA range

Output Noise Spectral Density

0.5

nA/√Hz

Measured at 10 kHz, midscale output, 0

mA to 24 mA range

1 Guaranteed by design and characterization; not production tested.

TIMING CHARACTERISTICS

AVDD = VBOOST_x= 15 V; DVDD = 2.7 V to 5.5 V; AVCC = 4.5 V to 5.5 V; dc-to-dc converter disabled; AGND = DGND = GNDSWx = 0 V;

REFIN = 5 V; RL = 300 ; all specifications TMIN to TMAX, unless otherwise noted.

Table 3.

Parameter1, 2, 3

Limit at T

MIN, TMAX

Unit

Description

t

1

33

ns min

SCLK cycle time

t

2

13

ns min

SCLK high time

t

3

13

ns min

SCLK low time

t

4

13

ns min

SYNC falling edge to SCLK falling edge setup time

t

5

13

ns min

t

6

198

ns min

SYNC high time

t

7

5

ns min

Data setup time

t

8

5

ns min

Data hold time

t

9

20

s min

SYNC rising edge to LDAC falling edge (all DACs updated or any channel has

digital slew rate control enabled)

5

s min

SYNC rising edge to LDAC falling edge (single DAC updated)

t

10

ns min

LDAC pulse width low

t

11

500

ns max

LDAC falling edge to DAC output response time

t

12

See the AC Performance

Characteristics section

s max

DAC output settling time

t

13

10

ns min

CLEAR high time

t

14

5

s max

CLEAR activation time

t

15

40

ns max

SCLK rising edge to SDO valid

t

16

21

s min

SYNC rising edge to DAC output response time (LDAC = 0) (all DACs updated)

5

s min

SYNC rising edge to DAC output response time (LDAC = 0) (single DAC updated)

t

17

500

ns min

LDAC falling edge to SYNC rising edge

t

18

800

ns min

RESET pulse width

t

19

20

s min

SYNC high to next SYNC low (digital slew rate control enabled) (all DACs updated)

5

s min

SYNC high to next SYNC low (digital slew rate control disabled) (single DAC

updated)

1 Guaranteed by design and characterization; not production tested.

2 All input signals are specified with t

RISE = tFALL = 5 ns (10% to 90% of DVDD) and timed from a voltage level of 1.2 V.

4 This specification applies if LDAC is held low during the write cycle; otherwise, see t

9.

相关PDF资料 |

PDF描述 |

|---|---|

| MS3122E16-23S | CONN RCPT 23POS BOX MNT W/SCKT |

| MS27497T18A32PLC | CONN HSG RCPT 32POS WALL MT PINS |

| AD7225KNZ | IC DAC 8BIT QUAD W/AMP 24DIP |

| VE-2WL-MY-F4 | CONVERTER MOD DC/DC 28V 50W |

| AD7537KRZ | IC DAC 12BIT DUAL MULT 24SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5757ACPZ-REEL7 | 功能描述:IC DAC 16BIT QUAD IOUT 64LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k |

| AD5757X | 制造商:AD 制造商全称:Analog Devices 功能描述:Quad Channel, 16-Bit, Serial Input, 4-20mA Output DAC, Dynamic Power Control, HART Connectivity |

| AD575JD | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 10-Bit |

| AD575JN | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 10-Bit |

| AD575KD | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 10-Bit |

发布紧急采购,3分钟左右您将得到回复。