- 您现在的位置:买卖IC网 > PDF目录373890 > AD6623ABC (ANALOG DEVICES INC) 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP PDF资料下载

参数资料

| 型号: | AD6623ABC |

| 厂商: | ANALOG DEVICES INC |

| 元件分类: | 通信及网络 |

| 英文描述: | 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PBGA196 |

| 封装: | CSPBGA-196 |

| 文件页数: | 29/40页 |

| 文件大小: | 381K |

| 代理商: | AD6623ABC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

REV. 0

AD6623

–29–

Single-Carrier Scaling

Once the optimal power level is determined for each carrier, one

must determine the best way to achieve that level. The maximum

SNR can be achieved by maximizing the intermediate power level

at each processing stage. This can be done by assuming the proper

level at the output and working along the following path: Sum-

mation, NCO, CIC, Ramp, RCF, and finally, Fine Scaler Unit.

The Summation Block is intended to combine multiple carriers

with each carrier at least 6 dB below full scale. For this configu-

ration, the AD6623 driving the DAC should have clip detection

enabled. OUT17 becomes a clip indicator that reports clipping

in both polarities. If the DAC requires offset binary outputs, then

the internal offset binary conversion should be enabled as well.

Any preceding cascaded AD6623s should disable clip detection

and offset binary conversion. The IN17

–

IN0 of the first AD6623

in the cascade should be grounded. See the Summation Block

section for details. In this configuration, intermediate OUT17s will

serve as guard bits that allow intermediate sums to exceed full scale.

As long as the final output does not exceed 6 dB over full scale, the

clip detector will perform correctly.

If a single carrier needs to exceed

–

6 dB full scale, hardwired

scaling can be accomplished according to Table XX. This is most

useful when the AD6623 is processing a Single Wideband

Carrier

such as UMTS or CDMA 2000.

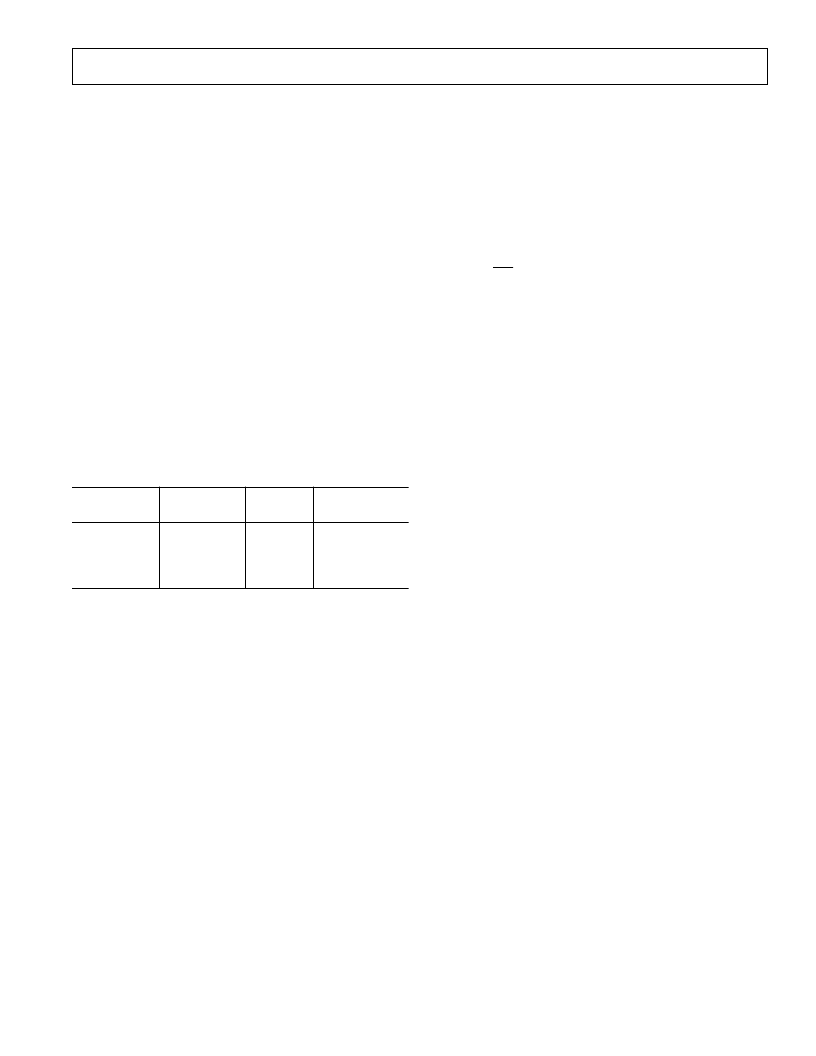

Table XX. Hardwired Scaling

Max. Single

Carrier Level

Connect to

DAC MSB

Clip

Detect

Offset Binary

Compensation

–

12.04 dB

–

6.02 dB

0 dB

+6.02 dB

OUT17

OUT16

OUT15

OUT14

N/A

±

+ only

+ only

Internal

Internal

0x08000

0x0C000

The NCO/Tuner is equipped with an output scaler that ranges

from

–

6.02 dB to

–

24.08 dB below full scale, in 6.02 dB steps. See

the NCO/Tuner section for details. The best SNR will be achieved

by maximizing the input level to the NCO and using the largest

possible NCO attenuation. For example, to achieve an output

level

–

20 dB below full scale, one should set the CIC output level to

–

1.94 dB below full scale and attenuate by

–

18.06 dB in the NCO.

The CIC is equipped with an output scaler that ranges from 0 dB

to

–

186.64 dB below full scale in 6.02 dB steps. This large attenuation

is necessary to compensate for the potentially large gains associ-

ated with CIC interpolation. See the CIC section for details. For

example to achieve an output level of

–

1.94 dB below full scale,

with a CIC5 interpolation of 27 (114.51 dB gain) and a CIC2 inter-

polation of 3 (9.54 dB gain), one should set the CIC_Scale to 20

and the Fine Scale Unit output level to

–

5.59 dB below full scale.

–

.

1 94

The ramp unit when bypassed will have exactly 0 dB of gain and

can be ignored. When in use, the gain is dependant on what value

is stored in the last valid RMEM location. RMEM words are

14 bits [0

–

1), so when the value is positive full scale, the gain is

about

–

0.0005 dB; probably neglectable.

The RCF coefficients should be normalized to positive full scale.

This will yield the greatest dynamic range. The RCF is equipped

with an output scaler that ranges from 0 dB to

–

18.06 dB below

full scale in 6.02 dB steps. This attenuation can be used to partially

compensate for filter gain in the RCF. For example, if the maximum

–

.

9 54

–

.

.

–

.

5 59

114 51 20

6 02

×

=

(22)

gain of the RCF coefficients is 11.26 dB, the RCF coarse scale

should be set to 2 (12.04 dB). This yields an RCF output level

and fine scale input level of

–

0.78 dB

11 26

.

The fine scale unit is left to turn a

–

0.78 dB level into a

–

5.59 dB

level. This requires a gain of

–

4.81 dB, which corresponds to a

14-bit [0

–

2] scale value of 1264h. All subsequent rescalings

during chip operation should be relative to this maximum.

12 04

.

0 78

–

.

–

=

(23)

–

.

5 59

–

.

0 78

–

.

4 81

=

(24)

floor

h

10

2

1264

4 81

20

13

–

.

×

=

(25)

Finally, as described in the RCF section, there may be a worst-case

peak of a phase that is larger than the channel center gain. In the

preceding example, if the worst case to channel center ratio is larger

than 4.59 dB (potentially overflowing the RCF), then the RCF_

Coarse_Scale should be reduced by one and the CIC_Scale should

be increased by one. In the preceding example, if the worst

case to

channel center ratio is larger than 5.59 dB (potentially over

flowing

the RCF and CIC), then the RCF_Coarse_Scale should be reduced

by one and the NCO_Output_Scale should be increased

by one.

MICROPORT INTERFACE

The MicroPort interface is the communications port between the

AD6623 and the host controller. There are two modes of bus

operation: Intel nonmultiplexed mode (INM), and Motorola non-

multiplexed mode (MNM) that is set by hard-wiring the MODE

pin to either ground or supply. The mode is selected based on the

use of the MicroPort control lines (DS or RD, DTACK or RDY,

RW or WR) and the capabilities of the host processor. See the

timing diagrams for details on the operation of both modes.

The External Memory Map provides data and address registers

to read and write the extensive control registers in the Internal

Memory Map. The control registers access global chip functions

and multiple control functions for each independent channel.

MicroPort Control

All accesses to the internal registers and memory of the AD6623

are accomplished indirectly through the use of the microprocessor

port external registers shown in Table XXI. Accesses to the Exter-

nal Registers are accomplished through the 3 bit address bus (A[2:0])

and the 8-bit data bus (D[7:0]) of the AD6623 (MicroPort).

External Address [3:0] provides access to data read from or writ-

ten to the internal memory (up to 32 bits). External Address [0]

is the least significant byte and External Address [3] is the most

significant byte. External Address [4] controls the Sleep Mode

of each channel. External Address [5] controls the sync status of

each channel. External Address [7:6] determines the Internal

Address selected and whether this address is incremented after

subsequent reads and/or writes to the internal registers.

EXTERNAL MEMORY MAP

The External Memory Map is used to gain access to the Internal

Memory Map described below. External Address [7:6] sets the

Internal Address to which subsequent reads or writes will be per-

formed. The top two bits of External Address [7] allow the user

to set the address to auto increment after reads, writes, or both.

All internal data words have widths that are less than or equal to

32 bits. Accesses to External Address [0] also triggers access to

the AD6623

’

s internal memory map. Thus during writes to the

相关PDF资料 |

PDF描述 |

|---|---|

| AD6623AS | 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6623PCB | 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6624AS | Four-Channel, 80 MSPS Digital Receive Signal Processor (RSP) |

| AD6624A | Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

| AD6624AABC | Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6623ABCZ | 制造商:Analog Devices 功能描述:Signal Processor 196-Pin CSP-BGA |

| AD6623AS | 制造商:Analog Devices 功能描述:Signal Processor 128-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:4 CHANNEL, 104 MSPS DIGITAL TSP - Bulk |

| AD6623ASZ | 功能描述:IC TSP 4CHAN 104MSPS 128MQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

| AD6623BC/PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6623PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

发布紧急采购,3分钟左右您将得到回复。