- 您现在的位置:买卖IC网 > PDF目录373890 > AD6623ABC (ANALOG DEVICES INC) 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP PDF资料下载

参数资料

| 型号: | AD6623ABC |

| 厂商: | ANALOG DEVICES INC |

| 元件分类: | 通信及网络 |

| 英文描述: | 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PBGA196 |

| 封装: | CSPBGA-196 |

| 文件页数: | 30/40页 |

| 文件大小: | 381K |

| 代理商: | AD6623ABC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

REV. 0

AD6623

–30–

internal registers, External Address [0] must be written last to

insure all data is transferred. Reads are the opposite in that

External Address [0] must be the first data register read (after setting

the appropriate internal address) to initiate an internal access.

External Address [5:4] reads and writes are transferred immediately

to internal control registers. External Address [4] is the sleep register.

The sleep bits can be set collectively by the address. The sleep bits

can

be cleared by operation of start syncs (described below).

External Address [5] is the sync register. These bits are write only.

There are three types of syncs: start, hop, and beam. Each of these

can be sent to any or all of the four channels. For example, a write of

X0010100

would issue a start sync to channel C only. A write of

X1101111

would issue a beam sync and a hop sync to all channels.

The internal address bus is 12 bits wide and the internal data bus

is 32 bits wide. External address 7 is the UAR (Upper Address

Register) and stores the upper four bits of the address space in

UAR[3:0]. UAR[7:6] define the auto-increment feature. If Bit 6

is high, the internal address is incremented after an internal read.

If Bit 7 is high, the internal address is incremented after an internal

write. If both bits are high, the internal address in incremented

after either a write or a read. This feature is designed for sequential

access to internal locations. External address 6 is the LAR (Lower

Address Register) and stores the

lower 8 bits of the internal

address. External addresses 3 through

0 store the 32 bits of the

internal data. All internal accesses are two clock cycles long.

Writing to an internal location with a data width of 16 bits is

achieved by first writing the upper four bits of the address to bits

3 through 0 of the UAR (bits 7 and 6 of the UAR are written to

determine whether or not the auto increment feature is enabled).

The LAR is then written with the lower eight bits of the internal

address (it doesn

’

t matter if the LAR is written before the UAR as

long as both are written before the internal access). Since the data

width of the internal address is 16 bits, only data register 1 and data

register 0 are needed. Data register 1 must be written first because

the write to data register 0 triggers the internal access. Data register

0 must always be the last register written to initiate the internal write.

Reading from the MicroPort is accomplished in a similar manner.

The internal address is first written. A read from data register 0

activates the internal read, thus register 0 must always be read first

to initiate an internal read. This provides the 8 LSBs of the internal

read through the MicroPort (D[7:0]). Additional bytes are then

read by changing the external address (A[2:0]) and performing

additional reads. If data register 3 (or any other) is read before

data register 0, incorrect data will be read. Data register 0 must

be read first in order to transfer data from the core memory to the

external memory locations. Once the data register is read, the remaining

locations may be examined in any order.

Access to the external registers of Table XX is accomplished

in one of two modes using the

CS

,

DS

(

RD

), RW(

WR

), and

DTACK

(RDY) inputs. The access modes are Intel Nonmulti-

plexed mode and Motorola Nonmultiplexed mode. These modes

are controlled by the MODE input (MODE = 0 for INM,

MODE

= 1 for MNM).

Intel Nonmultiplexed Mode (INM)

MODE must be tied low to operate the AD6623 MicroPort in

INM mode. The access type is controlled by the user with the

chip select (

CS

), read (

RD

), and write (

WR

) inputs. The ready

(RDY) signal is produced by the MicroPort to communicate to

the user the MicroPort is ready for an access. RDY goes low at

the start of the access and is released when the internal cycle is

complete. See the timing diagrams for both the read and write

modes in the Specifications.

Motorola Nonmultiplexed Mode (MNM)

MODE must be tied high to operate the AD6623

MicroPort

in

MNM mode. The access type is controlled by the user with the

chip select (

CS

), data strobe (

DS

), and read/write (RW) inputs.

The data acknowledge (

DTACK

) signal is produced by the

MicroPort to acknowledge the completion of an access to the user.

DTACK

goes low when an internal access is complete and then

will return high after

DS

is deasserted. See the timing diagrams

for both the read and write modes in the Specifications.

The

DTACK

(RDY) pin is configured as an open drain so that

multiple devices may be tied together at the microprocessor/

microcontroller without contention.

The MicroPort of the AD6623 allows for multiple accesses while

CS

is held low (

CS

can be tied permanently low if the MicroPort

is not shared with additional devices). The user can access multiple

locations by pulsing the RW(

WR

) or

DS

(

RD

) lines and changing

the contents of the external three bit address bus (A[2:0]).

External Address 7 Upper Address Register (UAR)

Sets the four most significant bits of the internal address, effectively

selecting channels 1, 2, 3, or 4 (D2:D0). The autoincrement of

read and write are also set (D7:D6).

External Address 6 Lower Address Register (LAR)

Sets the internal address 8 LSBs (D7:D0).

External Address 5 Sync

This register is write only. Bits in this address control the synchro-

nization of the AD6623 channels. If the user intends to bring up

channels with no synchronization requirements then all bits of this

register should be written low. Two types of sync signals are available

with the AD6623. The first is Soft Sync. Soft Sync is software

synchronization enabled through the MicroPort. The

second

synchronization method is Pin Sync. Pin Sync is enabled

by a signal

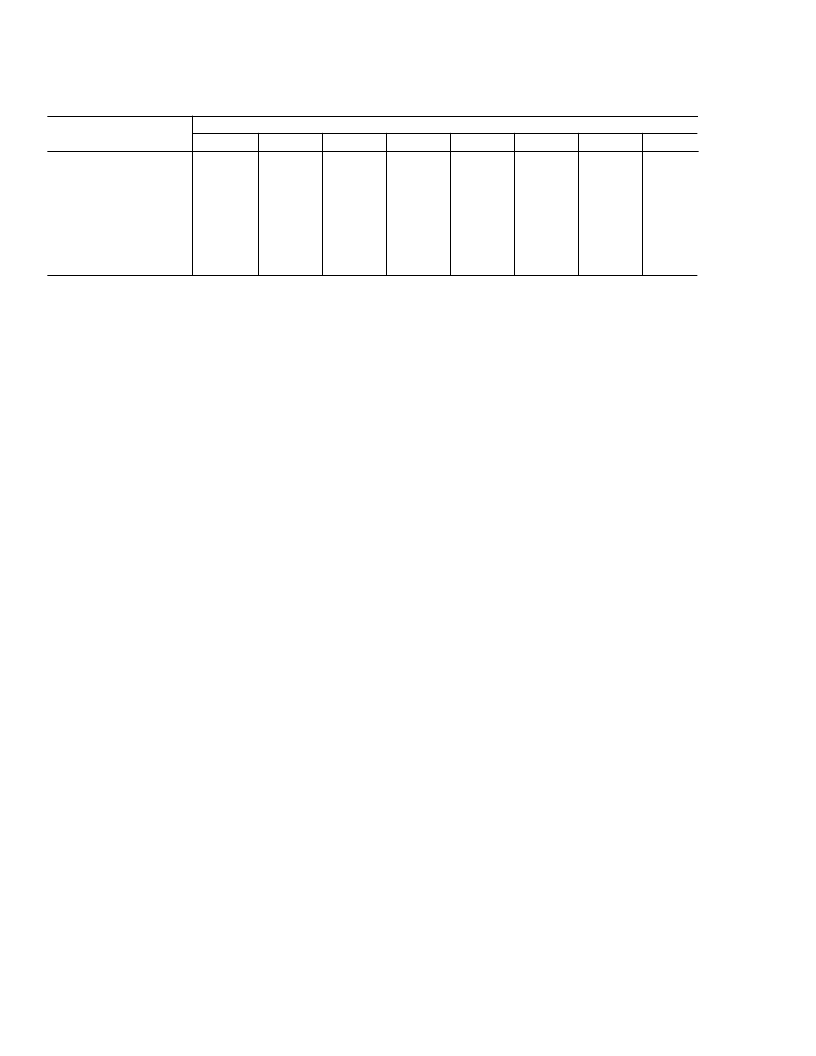

Table XXI. External Registers

External Data

D4

External Address

D7

D6

D5

D3

D2

D1

D0

7:UAR

6:LAR

5:Sync

4:Sleep

3:Byte3

2:Byte2

1:Byte1

0:Byte0

Wrinc

IA7

–

Prog D

ID31

ID23

ID15

ID7

Rdinc

IA6

Beam

Prog C

ID30

ID22

ID14

ID6

–

IA5

Hop

Prog B

ID29

ID21

ID13

ID5

–

IA4

Start

Prog A

ID28

ID20

ID12

ID4

IAII

IA3

Sync D

Sleep D

ID27

ID19

ID11

ID3

IAIO

IA2

Sync C

Sleep C

ID26

ID18

ID10

ID2

IA9

IA1

Sync B

Sleep B

ID25

ID17

ID9

ID1

IA8

IA0

Sync A

Sleep A

ID24

ID16

ID8

ID0

相关PDF资料 |

PDF描述 |

|---|---|

| AD6623AS | 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6623PCB | 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6624AS | Four-Channel, 80 MSPS Digital Receive Signal Processor (RSP) |

| AD6624A | Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

| AD6624AABC | Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6623ABCZ | 制造商:Analog Devices 功能描述:Signal Processor 196-Pin CSP-BGA |

| AD6623AS | 制造商:Analog Devices 功能描述:Signal Processor 128-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:4 CHANNEL, 104 MSPS DIGITAL TSP - Bulk |

| AD6623ASZ | 功能描述:IC TSP 4CHAN 104MSPS 128MQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

| AD6623BC/PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6623PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

发布紧急采购,3分钟左右您将得到回复。