- 您现在的位置:买卖IC网 > PDF目录373890 > AD6623AS (ANALOG DEVICES INC) 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP PDF资料下载

参数资料

| 型号: | AD6623AS |

| 厂商: | ANALOG DEVICES INC |

| 元件分类: | 通信及网络 |

| 英文描述: | 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP128 |

| 封装: | PLASTIC, MQFP-128 |

| 文件页数: | 16/40页 |

| 文件大小: | 381K |

| 代理商: | AD6623AS |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

REV. 0

AD6623

–16–

PROGRAMMABLE RAM COEFFICIENT FILTER (RCF)

Each channel has a fully independent RAM Coefficient Filter (RCF).

The RCF accepts data from the Serial Port, processes it, and passes

the resultant I and Q data to the CIC filter. A variety of processing

options may be selected individually or in combination,

including

PSK and MSK modulation, FIR filtering, all-pass phase equalization,

and scaling with arbitrary ramping. See Table III.

Table III. Data Format Processing Options

Processing Block

Input Data

Output Data

Interpolating FIR Filter

PSK Modulator

I and Q

2 or 3 bits

per symbol

I and Q

Unfiltered I

and Q:

/4-QPSK,

8-PSK, or

3 /8-8-PSK

Filtered MSK

or GSM I and Q

Filtered QPSK

I and Q

I and Q

I and Q

MSK Modulator

1 bit per symbol

QPSK

2 bits per symbol

All-pass Phase Equalizer

Scale and Ramp

I and Q

I and Q

OVERVIEW OF THE RCF BLOCKS

The Serial Port passes data to the RCF with the appropriate

format and bit precision for each RCF configuration, see Figure 17.

The data

may be modulated vectors or unmodulated bits. I and

Q vectors

are sent directly to the Interpolating Fir Filter. Unmodu-

lated bits may be sent to the PSK Modulator, the Interpolating

MSK Modulator, or the Interpolating QPSK Modulator. The PSK

Modulator produces unfiltered I and Q vectors at the symbol

rate which are then passed through the Interpolating FIR Filter.

The Interpolating MSK Modulator and the Interpolating QPSK

Modulator produce oversampled, pulse-shaped vectors directly

without employing the Interpolating FIR Filter. When possible,

the MSK and QPSK modulators

are recommended for increased

throughput and decreased power

consumption compared to

Interpolating FIR Filter. In addition, the Interpolating MSK

Modulator can realize filters with nonlinear inter-symbol inter-

ference, achieving excellent accuracy for GMSK applications.

After interpolation, an optional Allpass Phase Equalizer (APE)

can be inserted into the signal path. The APE can realize any real,

stable, two-pole, two-zero all-pass filter at the RCF

’

s interpolated

rate. This is especially useful to precompensate for nonlinear

phase responses of receive filters in terminals, as specified by IS-95.

When active, the APE utilizes shared hardware with the interpo-

lating modulators and filter, which may reduce the allowed RCF

throughput, inter-symbol interference, or both. See Figure 18.

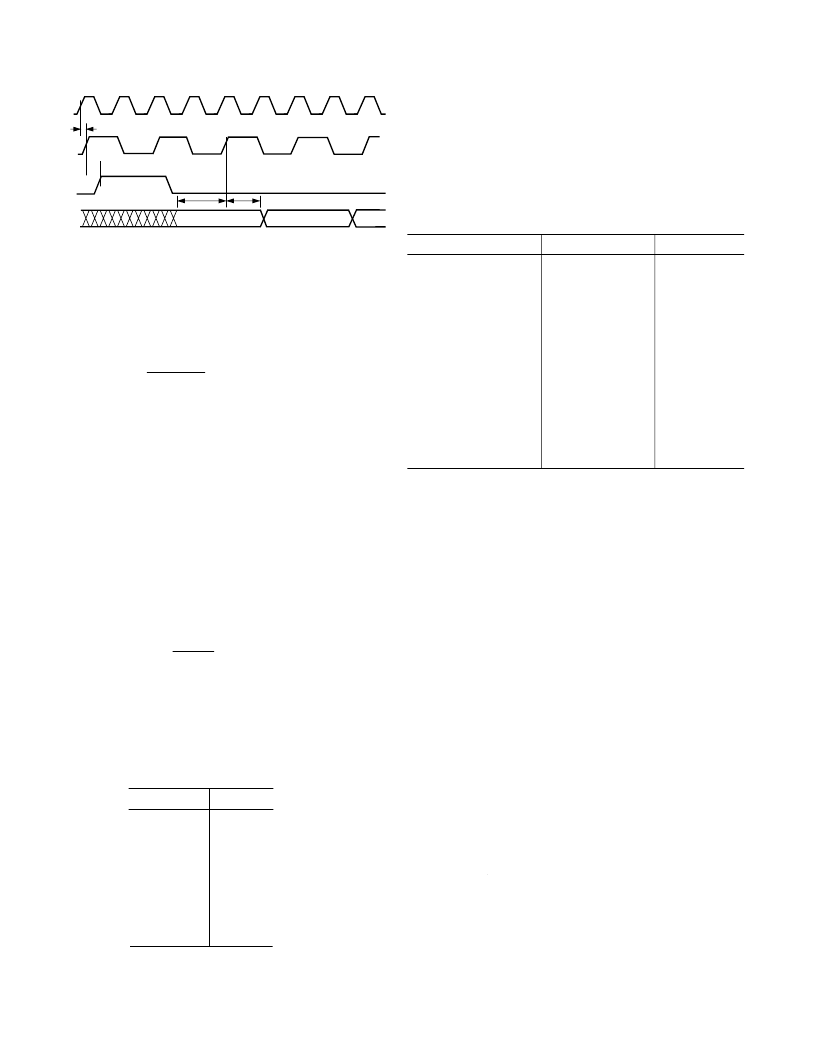

t

DSDFO0A

t

HSDI0

SCLK

SDFO

SDI

DATAn

CLK

t

SSDI0

CLKn

t

SSDI0

Figure 16. Serial Port Switching Characteristics

As an example of the Serial Port operation, consider a CLK fre-

quency of 62.208 MHz and a channel interpolation of 2560. In

that case, the input sample rate is 24.3 kSPS (62.208 MHz/2560),

which is also the SDFO rate. Substituting, f

SCLK

≥

32 f

SDFO

into the equation and solving for SCLKdivider, we find the mini-

mum

value for SCLKdivider according to the equation below.

SCLKdivider

f

×

f

CLK

SFDO

≤

32

(3)

Evaluating this equation for our example, SCLKdivider must be

less than or equal to 79. Since the SCLKdivider channel register

is a 5-bit unsigned number it can only range from 0 to 31.

Any value in that range will be valid for this example, but if it is

important that the SDFO period is constant, then there is another

restriction. For regular frames, the ratio f

SCLK

/f

SDFO

must be equal

to an integer of 32 or larger. For this example, constant SDFO

periods can only be achieved with an SCLK divider of 31 or less.

See Table II for usable SCLK divider values and the corresponding

SCLK and f

SCLK

/f

SDFO

ratio for the example of L = 2560.

In conclusion, SDFO rate is determined by the AD6623 CLK

rate and the interpolation rate of the channel. The SDFO

rate is

equal to the channel input rate. The channel interpolation

is

equal to RCF interpolation times CIC5 interpolation, times

CIC2 interpolation:

L

L

L

L

M

RCF

CIC

CRIC

CRIC

=

×

×

5

2

2

(4)

The SCLK divide ratio is determined by SCLKdivider as shown

in the previous equation. The SCLK must be fast enough to

input 32 bits of data prior to the next SDFO. Extra SCLKs are

ignored by the serial port.

Table II. Example of Usable SCLK Divider

Values and f

SCLK

/f

SDPO

Ratios for L = 2560

SCLKdivisor

f

SCLK

/f

SDFO

2560

1280

640

512

320

256

160

128

80

0

1

3

4

7

9

15

19

31

相关PDF资料 |

PDF描述 |

|---|---|

| AD6623PCB | 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6624AS | Four-Channel, 80 MSPS Digital Receive Signal Processor (RSP) |

| AD6624A | Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

| AD6624AABC | Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

| AD6630AR-REEL | Differential, Low Noise IF Gain Block with Output Clamping |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6623ASZ | 功能描述:IC TSP 4CHAN 104MSPS 128MQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

| AD6623BC/PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6623PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| AD6623S/PCB | 制造商:Analog Devices 功能描述:4-CH, 104 MSPS DGTL TRANSMIT SGNL PROCESSOR (TSP) 28SOIC - Bulk |

| AD6624 | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 80 MSPS Digital Receive Signal Processor (RSP) |

发布紧急采购,3分钟左右您将得到回复。